# Eventide's harmonizer model H949

INSTRUCTION MANUAL

# Eventide's harmonizer model H949

ONE OCTAVE UP, TWO OCTAVES DOWN PITCH CHANGE TWO OUTPUTS, EACH WITH UP TO 400 MILLISECONDS OF DELAY MICRO PITCH CHANGE, FOR EXTREMELY PRECISE, STABLE SETTINGS FREQUENCY RESPONSE 15 KH7 LONG DELAY PERMITS SIMULATED REVERB FLANGING RANDOMIZED DELAY REPEAT \* TIME REVERSAL HIGH AND LOW FEEDBACK EQUALIZATION 96 DB DYNAMIC RANGE

TWO SELECTABLE ALGORITHMS, TO OMPIMIZE PITCH CHANGE PERFORMANCE DUAL COLOR LED'S FOR FRONT PANEL READABILITY SWITCHABLE 115/230 VOLTS

'... an almost endless variety of functions.' (Broadcast Management/Engineering) '... a new collection of effects at a most moderate cost.' (Studio Sound)

The Eventide model H949 Harmonizer is a combination digital delay line, pitch changer, and all-round special effects unit. The TIME REVERSAL feature is entirely new. When used with a variable-speed tape recorder, the Harmonizer is capable of shortening or lengthening a piece of program material to fit a given time slot, without altering the pitch. The H949 is built to professional industry standards, using random access memories (RAM's) for high quality, dependable performance.

# Eventide specifications:

## MODEL H949 HARMONIZER

INPUT CHARACTERISTICS

Impedance nominal 10 k, balanced, maximum level +24 dBm. Level for full dynamic range is from -10 dBm to +24 dBm.

OUTPUT CHARACTERISTICS

Impedance nominal 150 ohms. Suitable for driving 600 ohms or greater at +18 dBm. Electronically balanced.

DISTORTION

Less than .15% at 1 kHz, reference output level.

DYNAMIC RANGE

Greater than 96 dB from clipping to noise floor.

PITCH VARIATION

1 octave up, 2 octaves down, continuously variable. Four-digit readout indicates precise ratio.

DELAY

Main output - in Pitch Change mode: 0 to 300 ms in 50 ms steps. In Delay mode: 0 to 393.75 ms in 6.25 ms steps. Delay Only output: 0 to 393.75 ms in 6.25 ms steps.

FREQUENCY RESPONSE

At any delay, unity pitch ratio: 20 Hz to 15 kHz,  $\pm 1$  dB. No degradation with increasing delay.

SIZE

Requires 8.89 cm  $(3\frac{1}{2})$  x 48.26 cm (19) panel space. Extends 29.85 cm (11-3/4) behind panel.

POWER REQUIREMENTS

Switchable between 115 VAC (105 - 120 VAC), 50 - 60 Hz, and 230 VAC (220 - 240 VAC), 50 - 60 Hz. Nominal power dissipation 45 watts.

REMOTE CONTROL

Provision has been made for control by microcomputer using the IEEE standard interface bus (IEEE 488/1975). The HK940 keyboard can be used to control the pitch ratio in discrete musical steps. Option 05 mono keyboard controls one Harmonizer; option 06 polyphonic keyboard controls up to three Harmonizers.

An input is provided to phase-lock the Harmonizer to any synthesizer. A 3 volt peak-to-peak signal is required. The pitch may be varied by a control voltage input in the 5 to 15 volt range (internally selected).

CAUTION WARNING BEWARE CAVEAT EMPTOR WATCH OUT READ THIS NOTICE N.B.

Like all pitch changers using time speed-up/slow-down techniques, the Harmonizer produces certain artifacts or 'glitches' in the output during pitch change operation. The relative audibility and severity of these artifacts depend upon many factors, including the pitch ratio and the nature of the program material. The Model H949 Harmonizer has been designed with two different algorithms, allowing the user to choose which sounds best for the particular application. Because judgement of the performance of the Harmonizer is, in the final analysis, very subjective, we suggest that you try the Harmonizer before buying one. This warning does not apply to the Delay mode, in which the unit works just fine.

# TABLE OF CONTENTS

|                                                           |        | page  |       |

|-----------------------------------------------------------|--------|-------|-------|

| Limited Warranty                                          | Inside | front | cover |

| Warranty Form                                             |        | i.    |       |

| General Description                                       |        | iii.  |       |

| Specifications                                            |        | iv.   |       |

| Table of Contents                                         |        | 1.    |       |

| Introduction                                              |        | 1.    |       |

| CONTROL DESCRIPTION                                       |        | 2.    |       |

| Both Outputs:                                             |        |       |       |

| Power On/Off                                              |        | 2.    |       |

| Line In/Out                                               |        | 2.    |       |

| Input Level Control and Indicator Group                   |        | 3.    |       |

| Repeat Control                                            |        | 3.    |       |

| Feedback Control Group                                    |        | 3.    |       |

| Delay Only Output:                                        |        |       |       |

| Delay Only Output (msec) Switch Group                     |        | 4.    |       |

| Main Output:                                              |        |       |       |

| Pitch Control/Readout Group                               |        | 4.    |       |

| Function Select Switch Group                              |        | 5.    |       |

| Pitch Control Group (red)                                 |        | 6.    |       |

| Delay/Random/Flange/Reverse Functions (green)             |        | 7.    |       |

| Main Output (msec) Delay Set Switch Group                 |        | 8.    |       |

| Algorithm Select 1/2                                      |        | 8.    |       |

| Remote Control                                            |        | 9.    |       |

| Voltage Control of Pitch Ratio                            |        | 9.    |       |

| Resistive Control of Pitch Ratio                          |        | 10.   |       |

| Frequency Control of Pitch Ratio                          |        | 10.   |       |

| Rear Panel Connectors:                                    |        |       |       |

| AC Power Connector                                        |        | 11.   |       |

| Input Connector                                           |        | 11.   |       |

| Output Connectors                                         |        | 11.   |       |

| Keyboard Connector, Remote Control (IEEE/488) connector - |        |       |       |

| refer to Keyboard and Remote Control Sections             |        |       |       |

| Capstan Drive and External Control Terminal Strip         |        | 11.   |       |

| Grounding                                                 |        | 11.   |       |

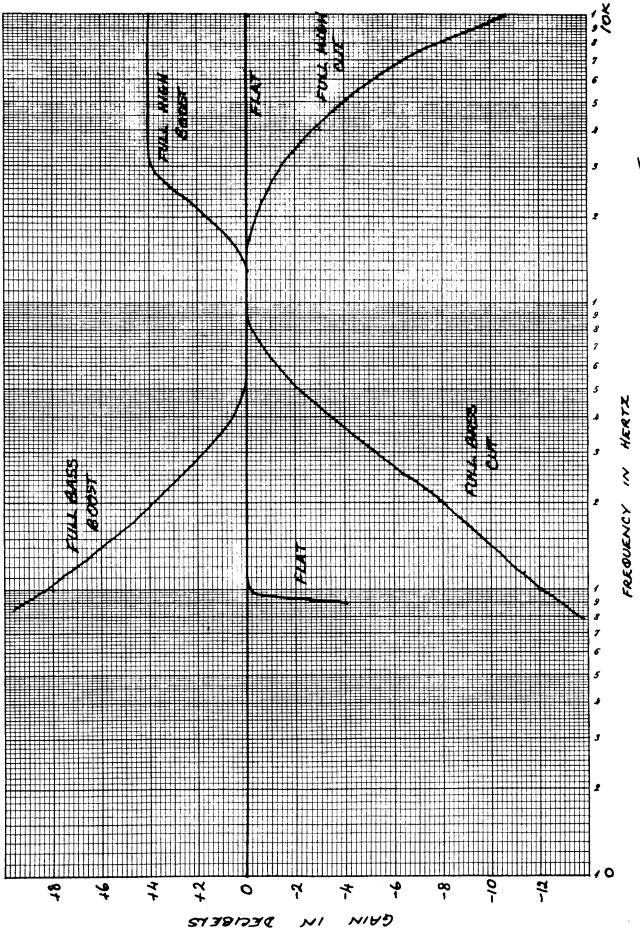

| Feedback Equalization Frequency Response                  |        | 12.   | •     |

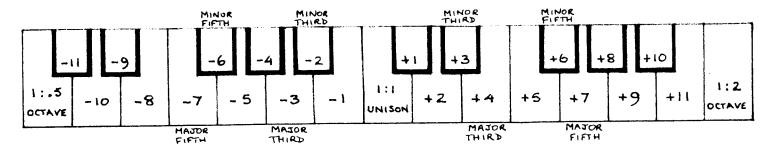

| Pitch Ratio Readouts for Various Musical Relationships    |        | 13.   |       |

| Pitch Change                                              |        | 13.   |       |

| Tempo Regulation                                          |        | 13.   |       |

| Things Not To Worry About                                 |        | 14.   |       |

| HK940 Keyboard                                            |        | 15.   |       |

| Use of the HK940 Keyboard with Model H949 Harmonizer      |        | 15.   |       |

| Interconnection of HK940 Keyboard with H910 and H949      |        | 16.   |       |

There is a separate Technical Section, with its own Table of Contents.

# INTRODUCTION

The Eventide model H949 Harmonizer has a great many functions and modes of operation, which may seem confusing at first. We recommend that you spend some time familiarizing yourself with the different things the unit can do.

H949 page 2.

**INSTALLATION**

The H949 will operate best in a well-ventilated location. If the unit is going to be subject to vibration (when traveling, for example) we recommend some support for the rear of the unit, not just rack mounting.

LINE VOLTAGE

See section below. It is very easy to change the H949 from 115 to 230 volts. Remember that while applying 115 volts to a unit set for 230 will not hurt it (it won't work, though), applying 230 volts to a unit set for 115 may well prove disastrous. Check again when the unit goes along on your world tour.

CONNECTION

The Harmonizer needs to be supplied with line level - if you are feeding it from a microphone, guitar, or similar, you will need a preamp. Connect the AC power cord, the input and output connectors, then set the front panel controls as shown below. This is a simple setting which will enable you to change the pitch of the input signal by turning the MANUAL knob. After that - experiment!

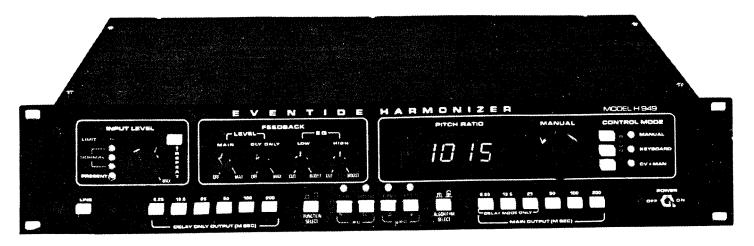

# CONTROL DESCRIPTION

This section describes the various operating controls and front panel indicators of the Harmonizer model H949. Because of the large number of operating modes, many of the controls have multiple functions, and interact in unexpected ways. To avoid multiple cross references, the multimode controls may be partially described under more than one heading. Please be sure to read and understand the operation of all the operating controls before using the Harmonizer.

#### POWER ON/OFF

CAUTION: Before operating this control, be sure that the Harmonizer is set to the AC power line voltage appropriate for your location. As detailed in the Specifications, the 949 will operate at 115 VAC (105 - 120 VAC) and 230 VAC (220 - 240 VAC). If your local line voltage is consistently lower than these ranges, a step-up transformer may be necessary. If your local power line is subject to significant fluctuations, it will be advisable to use a voltage regulating transformer.

The POWER control applies AC power to the Harmonizer. No power is consumed when in the OFF position.

#### LINE IN/OUT

This control switches the Harmonizer IN and OUT of the audio circuit to which it is connected. When the control is IN (physically depressed), the Harmonizer INPUT is connected to the internal circuitry, and the two OUTPUTS are connected to their respective output amplifiers. When the switch is OUT the Harmonizer INPUT is directly connected to the two OUTPUT jacks and all the Harmonizer circuitry is bypassed.

The MAIN LEVEL control adjusts the feedback from the MAIN (pitch change/effect) output to the input.

The DLY ONLY LEVEL control adjusts the feedback from the DELAY ONLY output to the input. The outputs from both the MAIN and DLY ONLY LEVEL controls are mixed and applied to the EQ controls, which control the frequency response of the feedback chain.

The LOW EQ control adjusts the relative level of bass frequencies present in the feedback mix. When rotated counterclockwise, lows are cut; when rotated clockwise, they are boosted.

The HIGH EQ control has a corresponding effect on higher frequencies. When both controls are centered, the frequency response of the feedback chain is approximately flat.

The actual frequency corners and rolloff curves are available in the specifications section of this manual. Please note that one can set the FEEDBACK controls, deliberately or otherwise, to a point where loop gain exceeds 1 at various frequencies. It is possible, and even easy to obtain uncontrolled oscillation. For this reason, it is suggested that the operation of the FEEDBACK group be undertaken cautiously until the user is fully familiar with the possibilities for interaction of the various controls.

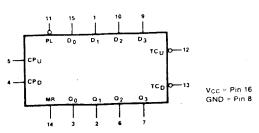

# DELAY ONLY OUTPUT (MSEC) SWITCH GROUP

This group of switches controls the delay time of the DELAY ONLY output. Each switch is a push/ON push/OFF control which is active when the button is depressed. The numbers above each switch represent the number of milliseconds (1/1000 second) added to the time delay when that switch is active. For instance, if buttons 1, 2, and 6 are in and buttons 3,4, and 5 are out, the time delay at the DELAY ONLY OUTPUT would equal 6.25ms+12.5ms+200ms, or 218.75 milliseconds.

The switches may be activated in any combination. The maximum obtainable delay is equal to the sum of all the switches, 393.75 milliseconds, or about four tenths of a second. Setting the delay of the DELAY ONLY OUTPUT has no effect on, and is not affected by, any settings of the delay or mode controls associated with the MAIN OUTPUT.

#### PITCH CONTROL/READOUT GROUP

This block of controls is associated primarily with the manual/remote control of the output pitch ratio of the MAIN OUTPUT vs. the input signal. Only the general function of the controls will be described here as the precise function varies depending upon the operating mode set by the FUNCTION SELECT switch group.

The MANUAL pitch ratio control is an analog control which sets the Harmonizer to the desired pitch ratio. In the NORMal pitch change mode, the range of this control is approximately 2 octaves down (decreased pitch) to 1 octave up. This control also determines the rate of delay change in the FLANGE and RANDOM modes. See the table following this section for the range of this control in the various operating modes.

The PITCH RATIO indicator is a four digit LED display which, in all modes other than DELAY, shows the numerical pitch ratio between the INPUT and the OUTPUT. This ratio may be converted to musical intervals (thirds, fifths, etc.) by reference to the table in the appendix. As with the MANUAL control, its range varies depending upon the FUNCTION SELECTED. It also provides additional information in the FLANGE and RANDOM modes by giving a visual indication of the operation and rate of both functions.

# PITCH CONTROL GROUP (RED)

When the FUNCTION SELECT is IN, the lower, RED labels of the function switches are effective. The leftmost switch, labelled "NORM", places the Harmonizer in the normal pitch change mode. Adjusting the MANUAL control over its full range gives pitch ratios from .25 (two octaves down) to 2.0 (one octave up. Note that the readout may exceed these ratios at the control extremes.

To assure adequate variation, the control is factory adjusted to provide extra range at each end. Although it is usually possible to dial ratios beyond the extremes given in the specifications, certain undesirable effects may become apparent: At the LOW end, decreasing the pitch ratio may increase the noise level, manifest symptoms of aliasing or heterodyning, and create other unpleasant digital sounding effects. At the HIGH end, increasing the reading beyond 2.00 will NOT increase the pitch ratio, but WILL create small amounts of undesirable phase noise.

The EXTENDED PC mode permits selection of the length of signal segment over which the pitch change algorithm operates. The NORM pitch change mode operates with a delay variation of approximately 25 milliseconds (see Theory of Operation). Depressing EXTEND allows extension of this segment to the full extent of the Harmonizer memory, or some fraction thereof, depending upon the setting of the MAIN OUTPUT (MSEC) DELAY (Normal operation of these switches is discussed under the next GROUP heading.) Special operations of these controls is also mentioned here, and under the REVERSE FUNCTION heading. When the rightmost three of these switches are physically OUT (normally inactive), the EXTENDED pitch memory segment covers the entire memory, 400 milliseconds. Depressing the 200 MILLISECOND (rightmost) switch cuts this memory segment by 200 milliseconds, to a total of 200 milliseconds. Depressing the 100 MILLISECOND switch (next to rightmost), the memory segment is DECREASED by 100 milliseconds, thus giving a total memory segment of 100 milliseconds. Depressing the 50 MILLISECOND switch decreases the memory segment to 50 milliseconds. Note that the operation of these switches may be regarded as reversed from their normal operation: Depressing the 200MS, 100MS and 50MS switches RESTRICTS the memory segment used by the pitch change mode by the amount indicated. If the 200MS switch is released (OUT), depressing the 100MS or 50MS switch will have no effect. If the 100MS switch is OUT, depressing the 50MS switch will have no effect.

UPC (MICRO PITCH CHANGE) modes, SHARP AND FLAT. These modes operate in a manner similar to the NORM PITCH CHANGE function, except that the range of pitch ratios is restricted to about 1:1.07 (SHARP) and 1:.93 (FLAT). Depressing the SHARP button allows adjustment of the pitch ratio from almost exactly 1:1 (unison) to approximately 1:1.07, corresponding to more than a musical "semitone". The pitch is adjusted using the MANUAL control, which now operates nonlinearly, so that as it is rotated closer to 1:1, the pitch change per degree of rotation decreases. This permits extremely fine and stable control of pitch ratios closer to unity. It is easily possible to obtain an adjustment of 1.001 to 1, and have this remain stable over time and temperature within .1 per cent. This is better than an order of magnitude improvement over previously available units.

Depressing the FLAT button gives an adjustment range of approximately 1:1 to 1:.93, or more than one "semitone" down. Again, as the ratio approaches 1:1, the sensitivity of the ratio to the knob rotation decreases.

Note: For both SHARP and FLAT operation of MICRO PITCH CHANGE, the PITCH RATIO is closest to 1:1 when the MANUAL control is fully counter-clockwise. In SHARP, clockwise rotation DECREASES the pitch. In FLAT, clockwise rotation DECREASES the pitch.

# DELAY/RANDOM/FLANGE/REVERSE FUNCTIONS (GREEN)

When the FUNCTION SELECT is OUT, the upper, GREEN labels of the function switches are effective. The first of these is the DELAY switch. When this switch is depressed, the MAIN OUTPUT acts like the DELAY ONLY output, and the IN/OUT pitch ratio remains at unity. The time delay is set by the MAIN OUTPUT (MSEC) switch group as described later.

Note: When in the DELAY mode, the MANUAL control affects the PITCH RATIO readout in the same manner as when the unit is in the NORM (PITCH CHANGE) mode. This is useful if one desires to pre-set the pitch ratio without changing the output signal: releasing the FUNCTION SELECT switch immediately acquires the selected pitch ratio. Remember: in the DELAY MODE, the pitch always remains at UNITY, regardless of other control settings or the PITCH RATIO readout.

#### RANDOM FUNCTION SELECT switch

Depressing this switch causes the MAIN OUTPUT to vary its delay between the maximum limits of 0 and 25 milliseconds at a constant rate of delay change. The actual delay limits, while restricted to the range given above, will typically be smaller on any given excursion. The range is determined in a "pseudo-random" manner by the Harmonizer's digital circuitry, and the effect created by using this mode closely simulates the random variations experienced when having individual performers "double" tracks, or having multiple musicians or singers performing simultaneously. Use of this operating mode is advantageous for "automatic double tracking" (ADT) because it gives a less "mechanical" sound than does fixed delay.

In the RANDOM MODE, the MANUAL pitch control varies the rate at which the delay varies from the upper to lower limit. Clockwise rotation increases the rate. Because the pitch varies slightly as the delay changes, the desirable effect of having the singers/performers very slightly out of tune is automatically achieved. The degree of pitch change may be reduced to a very small amount with the MANUAL control if so desired.

#### FLANGE FUNCTION Switch

This switch sets the Harmonizer into an automatic flanging mode. "Flanging" is the effect created when two signals of slightly differing delays are added together, while the delay of one signal is varying. (Delays on the order of 0 to 10 milliseconds are used. The lowest frequency affected is roughly the reciprocal of the time delay, so that a one millisecond delay causes cancellations at 1KHz and multiples thereof.) In the FLANGE mode, the MANUAL control varies the SWEEP rate, or the rate at which the delay of the variable delay signal is changing. Turning the MANUAL control clockwise increases the sweep rate.

Note: It is NO, recessary to mix the outputs of the MAIN and the DELAY ONLY outputs externally to achieve flanging. The DELAY ONLY output is unaffected by the FLANGE MODE, and the MAIN OUTPUT signal is flanged automatically.

#### RANDOM and FLANGE MODE NOTE:

To achieve normal FLANGING and RANDOM MODE operation, it is necessary for the ALGORITHM SELECT switch to be in the ALGORITHM 2 (physically OUT) position. If it is in the ALGORITHM 1 position, the output amplitude will vary with time and an extra delayed signal may be heard. The purpose of the ALGORITHM SELECT control is discussed later.

#### REVERSE FUNCTION switch

The final function switch controls the REVERSE mode of the Harmonizer. Activating

this mode causes the data entered into the memory to be read out backwards, so that short signal segments (up to the memory capacity of the Harmonizer) are presented in a time reversed order. The tape recorder analogy would be equivalent to cutting up a tape into 6 inch segments (at 15 inches per second) and then splicing the segments back into the same order after reversing the individual segments. Obviously this effect cannot reverse the time-order of entire programs as can playing a tape backwards, but the overall effect is the same except for signals which have very long attack or decay times.

The MANUAL pitch change control is active in the REVERSE mode and the pitch of the reversed signal may be altered within the same limits defined for the NORMal PITCH mode. There is no corresponding MICRO PITCH CHANGE mode for the REVERSE function.

Note that the REVERSE mode normally spans the entire Harmonizer memory of 400ms. If it is desired to reduce the length of signal segment acted upon by the reverse mode, one may restrict it by depressing the MAIN OUTPUT (MSEC) delay select switches as described in the EXTENDED PC mode. Depressing the 200MS button reduces the segment length to 200 milliseconds. Depressing the 100MS button reduces the segment length to 100 milliseconds, and depressing the 50MS button reduces the segment length to 50 milliseconds.

# MAIN OUTPUT (MSEC) DELAY SET SWITCH GROUP

This group of 6 push/ON push/OFF buttons controls the delay of the MAIN OUTPUT. Depending upon the FUNCTION SELECTED, the switches may have other effects (see EXTENDED PITCH mode and REVERSE mode.) In the DELAY mode, all of the switches are active, and they operate in a manner precisely analogous to the DELAY ONLY OUTPUT (MSEC) switch group described earlier. In the DELAY mode, the MAIN OUTPUT DELAY is equal to the sum of the individual switches depressed.

In the NORM, MICRO PC, RANDOM, and FLANGE modes, only the last three switches are active. This is because the delay variation required by these functions is greater than the small increments of delay otherwise permitted. The MAIN OUTPUT, WITH THE EFFECT SELECTED, will be displaced by 50 to 350 milliseconds from its normal location in time, in accordance with the buttons depressed.

#### ALGORITHM SELECT 1/2

The ALGORITHM SELECT control determines the method the Harmonizer employs to handle the "glitches" which are a theoretical and practical consequence of the pitch change process. The word "algorithm" is defined as a precise, describable process which acts upon or modifies inputs in a specific manner. An algorithm may be simple or complex, although it must be defined under all circumstances. The characteristics of the two algorithms are described in greater detail in the Theory of Operation section.

Algorithm 2 is similar to that used in the Eventide Model H910 Harmonizer. It is characterized by "glitches" which occur at increasing frequency as the pitch ratio deviates from 1:1. Algorithm 1 does not produce glitches, but there is a varying degree of signal "coloration". For pitch ratios below .5 (one octave), algorithm 2 may produce hard "glitches" or clicks, and so algorithm 1 should be used at such extreme pitch errors.

Note: The proper selection of pitch change algorithm is a significant factor in the degree of success with which one can expect to modify the pitch of performed or recorded material. We recommend experimentation as the final arbiter of which is appropriate for any given program material and pitch ratio. The two algorithms converge in audible effect as the pitch ratios approach an octave in either direction, and both will perform identically at these extremes.

| FUNCTION               | ALGORITHM | PITCH<br>RATIO | CONTROL<br>MODE |

|------------------------|-----------|----------------|-----------------|

| DELAY                  | -         | .25-2.00       | MAN,CV+M,KYBD   |

| RANDOM                 | 2 *       | .99-1.01       | MAN,CV+M        |

| FLANGE                 | 2 *       | .99-1.01       | MAN,CV+M        |

| REVERSE                | 1 OR 2    | .25-2.00       | MAN,CV+M,KYBD   |

| NORMAL<br>PITCH CHANGE | 1 OR 2    | .25-2.00       | MAN,CV+M,KYBD   |

| EXTENDED PITCH CHANGE  | 1 OR 2    | .25-2.00       | MAN,CV+M,KYBD   |

| MICRO PC<br>SHARP      | 1 OR 2    | 1.0-1.1        | MAN,CV+M        |

| MICRO PC<br>FLAT       | 1 OR 2    | 1.090          | MAN,CV+M        |

<sup>\*</sup> Using algorithm #1 adds an extra delay to the output.

H949 Harmonizer - Chart showing which algorithm, pitch ratio, and control modes are operative for different functions.

# REMOTE CONTROL

There will shortly be available a remote control option for the H949 which uses the IEEE/488 General Purpose Interface Bus to interface with a microcomputer. If information is not already printed in this manual, sending in the Warranty Card from the front of the manual will ensure that you are sent the information as soon as it becomes available.

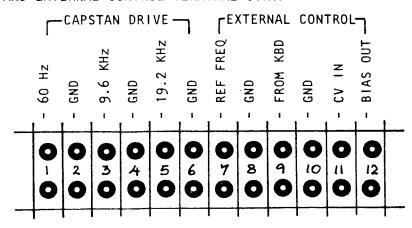

# VOLTAGE CONTROL OF PITCH RATIO

It is possible to remotely control the H949 Harmonizer pitch ratio by supplying a control voltage in the range from 0 ro +10 VDC. An internal adjustment allows setting of the control voltage full scale between +5 VDC and +10 VDC, making it compatible with various synthesizers. The control voltage should be applied between terminal strip pins 10 and 11, with pin 11 being more positive. Care should be taken to ensure that the control voltage is as pure and free of ripple as possible, to avoid frequency modulation of the pitch shifted signal.

For your convenience, a source of clean +12 volts, current limited by a 10 k resistor, is available at pin 12 of the terminal strip. The equivalent input circuit at the CV IN pin is a 10 k resistor in series with an operational amplifier non-inverting input. Therefore, voltages within the range 0 to +12 will be feeding

an essentially open circuit. Exceeding +12 volts will cause current to flow into the input, limited by the resistor. Greatly exceeding +12 volts may damage the input, and should be avoided.

Control voltage range adjustment

To adjust the external control voltage range, remove the Harmonizer top cover and swing the top board up on its hinges. The adjustment (labelled ECV LV) is a small trim resistor located about 3 cm in front of the keyboard Molex connector on the bottom circuit board.

### RESISTIVE CONTROL OF PITCH RATIO

A remote control may be provided simply by connecting a 100 k potentiometer between terminal strip pins 12 and 10 and connecting the wiper to pin 11. The unit is factory set so that this connection will cover a two-octave range. The front panel manual pitch ratio control will provide an offset, enabling this two-octave range to be selected from the three-octave range of the Harmonizer.

| 3-octave range of Harmonizer                                | 1:.25    | 1:.5             | 1:1        | 1:2 |

|-------------------------------------------------------------|----------|------------------|------------|-----|

| Potentiometer                                               |          | 2-octave ra      | nge        | \   |

| gives 2-octave<br>range, which can be<br>selected by offset | ( select | able between the | ese limits | )   |

Note: The maximum input voltage in this configuration is 10 volts.

### FREQUENCY CONTROL OF PITCH RATIO

In addition to voltage control, the Harmonizer may be externally varied in pitch ratio by applying an input frequency from a signal generator, synthesizer, or other source. This mode is preferable to the Control Voltage mode for musical applications as the input frequency is precisely related to the pitch ratio, i.e., if the input frequency is increased by one interval, the pitch ratio likewise increases by one interval.

Signal requirements

The input frequency must be spectrally pure in that only the fundamental and its harmonics may be present. The unit will not accept signals with more than one fundamental frequency present, and should not be driven by any source from which a clean, constant signal level cannot be guaranteed. Function generator/synthesizer waveforms such as sine, square, and triangle waves are all acceptable.

The input voltage should be at least 5 volts peak to peak for a sine wave, and at least 3 volts for a square wave. All standard logic families meet these requirements.

Input frequency for unit pitch ratio is 2.5 kHz. Increasing or decreasing the input frequency by up to one octave up, or two octaves down, produces a corresponding change in the pitch ratio.

Tuning

When using the Harmonizer with a customer-supplied keyboard, it may be necessary or desirable to re-tune the keyboard for a pitch ratio of 1.00 when middle C is depressed.

# REAR PANEL CONNECTIONS

AC POWER CONNECTOR

This connector accepts an internationally-approved IEC connector. The line cord furnished with the unit is for United States standard 3-wire outlets. The line voltage is specified on the serial number plate. It may be changed from 120 VAC to 240 VAC (or vice versa) by sliding the clear panel over the AC connector, removing the small printed circuit board, turning it round, reinserting it, and changing the fuse to the correct value ( $\frac{1}{2}$  amp for 120 VAC, 3/8 amp for 240 VAC, slo blo type).

INPUT CONNECTOR (3-pin XLR female)

This is the audio input connector for the H949 Harmonizer. Refer to the Specifications for levels and impedances.

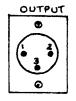

OUTPUT CONNECTORS (3-pin XLR male)

Each output has an output connector for audio.

Refer to the Specifications for levels and impedances.

Pin 1 is shield/chassis ground

Pin 2 is output - phase

pin 3 is output + phase

KEYBOARD CONNECTOR, REMOTE CONTROL (IEEE/488) CONNECTOR

Refer to Keyboard and Remote Control sections of manual for details.

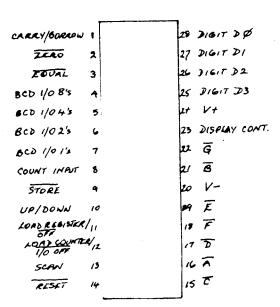

CAPSTAN DRIVE AND EXTERNAL CONTROL TERMINAL STRIP

#### GROUNDING

As with any piece of audio equipment, good grounding practices should be followed when connecting the unit. The grounds should be connected insofar as possible as shown above. This will help prevent ground loops and subtle troubles that can occur when equipment to be interconnected is at differing ground potentials. A sure sign of grounding problems is if an unexplained hum or buzz is present even when the LINE switch of the Harmonizer is in the OUT position. The LINE switch bypasses the unit with a DC path, and is independent of whether power is applied. While the Harmonizer is susceptible to certain faults and component breakdown, it is unlikely that generating hum or buzz is among them. If the unit seems to be contributing such a signal, and there is no evidence that the power supply is faulty, check your grounding scheme first of all. Incidentally, this applies to almost all accessory equipment.

EQUALIZATION FREQUENCY RESPONSÉ

| -3/4                                                                                         | -1/2                                                                                            | -1/4                                                                                         | NOTE                                                                                  | RELATIONSHIP                                                                                    | NOTE                                                                                                              | +1/4                                                                                                     | +1/2                                                                                                     | +3/4                                                                                                     |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| .958<br>.904<br>.853<br>.805<br>.760<br>.717<br>.677<br>.639<br>.603<br>.569<br>.537<br>.507 | .972<br>.917<br>.866<br>.817<br>.771<br>.728<br>.687<br>.648<br>.612<br>.578<br>.545<br>.515    | .986<br>.930<br>.878<br>.829<br>.782<br>.738<br>.697<br>.658<br>.620<br>.586<br>.553<br>.522 | 1.000<br>.944<br>.891<br>.841<br>.794<br>.749<br>.707<br>.667<br>.630<br>.595<br>.561 | UNISON  -1 +1  -2 +2  -3 +3  -4 +4  -5 +5  -6 +6  -7 +7  -8 +8  -9 +9  -10 +10  -11 +11  OCTAVE | 1.000<br>1.060<br>1.123<br>1.189<br>1.260<br>1.335<br>1.414<br>1.498<br>1.587<br>1.681<br>1.781<br>1.888<br>2.000 | 1.015<br>1.075<br>1.139<br>1.207<br>1.278<br>1.354<br>1.435<br>1.520<br>1.611<br>1.706<br>1.808<br>1.915 | 1.029<br>1.091<br>1.155<br>1.224<br>1.297<br>1.374<br>1.456<br>1.542<br>1.634<br>1.731<br>1.834<br>1.943 | 1.044<br>1.106<br>1.172<br>1.242<br>1.316<br>1.394<br>1.477<br>1.565<br>1.658<br>1.756<br>1.861<br>1.971 |

| .452<br>.427<br>.403<br>.380<br>.359<br>.339<br>.320<br>.302<br>.285<br>.269                 | . 459<br>. 433<br>. 407<br>. 381<br>. 364<br>. 344<br>. 324<br>. 306<br>. 289<br>. 273<br>. 257 | .465<br>.439<br>.414<br>.391<br>.369<br>.349<br>.329<br>.310<br>.293<br>.277<br>.261         | .472<br>.446<br>.420<br>.397<br>.375<br>.354<br>.334<br>.315<br>.297<br>.281<br>.265  | -13<br>-14<br>-15<br>-16<br>-17<br>-18<br>-19<br>-20<br>-21<br>-22<br>-23<br>TWO OCTAVES        | For us<br>Harmon                                                                                                  | The low vailable e with tizer, ro                                                                        | he H910<br>und off                                                                                       | e H949.<br>the                                                                                           |

#### PITCH CHANGE

The Eventide Harmonizers model H910 and H949, and 1745M Delay Line with Pitch Change Module may be used to generate musical harmonies by reference to the above table. Because a digital compression or stretching process is used, all harmonic relationships are preserved, unlike the disharmony produced by heterodyne-type 'frequency shifters'.

For example, suppose two frequencies, originally in a musical relationship, are shifted up by 100 Hz. Although the absolute difference between the signals remains constant, the musical interval between them decreases. However, if the two frequencies are multiplied by any constant, as in the Harmonizers and Pitch Change Module, the interval remains constant, even though the absolute difference will change.

#### TEMPO REGULATION

The internal oscillator of the 1745M and the H949 Harmonizer provides an output frequency which may be used to control the speed of a tape recorder. The H910 Harmonizer does not have this facility.

#### THINGS NOT TO WORRY ABOUT

This is a list of things which may seem strange but are really normal in the H949 Harmonizer.

- \* The rear panel regulator is exposed, yet mounted on a mica insulator. The insulator is to prevent hum in the output. THERE IS NO EXPOSED HIGH VOLTAGE on the regulator.

- \* When switching from PITCH to DELAY, it is not unusual to observe a small level shift (a fraction of a dB). This is of no consequence, either in operation or for maintenance. If the level shift exceeds 1 dB, it should be investigated. (See Alignment Section.)

- \* The PITCH RATIO READOUT will occasionally flash (blank) for a few milliseconds between readings. This is a characteristic of the counter chip, and should be ignored. Frequent blanking, several times in a ten-second period, may be indicative of a readout problem. This will RARELY IF EVER create an AUDIO problem.

- \* The LAST DIGIT of the readout will usually vary +/- one digit. This is a theoretical consequence of digital counting and does not indicate a corresponding variation in pitch ratio. In the UPC (micro pitch change) mode, the last digit may also DRIFT over time and temperature, and in the NORMAL PC mode, the second-from-last digit may drift over time and temperature. A variation of .1% in UPC and 1% in NORMAL PC is within tolerance. Excessive drift may be caused by unusually high line voltage, or lack of ventilation, or by defective components.

- Power line outages, or turning the Harmonizer OFF and then ON rapidly may initiat a mode of operation in which the UPC directions are reversed (flat becomes sharp) and FLANGE and RANDOM do not work. This occurs because the power ON reset circuitry requires time to discharge on power OFF. This problem may be remedied by turning the unit OFF for about five seconds before turning it ON again.

- \* The SIGNAL PRESENT LED does not go on at a precisely defined level, but rather is intended to show that a signal is present. It should always be OFF when the input level control is at zero, or there is no input signal (providing that the FEEDBACK controls are off). It should always be ON when the input signal exceeds -30 dB with respect to clipping. It may come ON at any level between these broad limits.

- \* It is possible, but very unlikely, for the PITCH CHANGE circuitry to go 'out of sync', introducing distortion at the main output. If this happens, the circuitry can be reset, either by changing the main output function, or by turning power OFF, waiting five seconds (see above) and then ON again.

- \* When operating in the External Control modes, the pitch ratio readout may indicate ratios above 2.00. However, the actual ratio will be limited to 2.00, regardless of the reading. Note that the pitch ratio readout continues to operate even in the DELAY mode. This is of advantage because it permits one to set a precise ratio and then switch from DELAY to that ratio by going into the PITCH CHANGE mode.

# HK940 - KEYBOARD FOR EVENTIDE HARMONIZER MODEL H910 AND MODEL H949

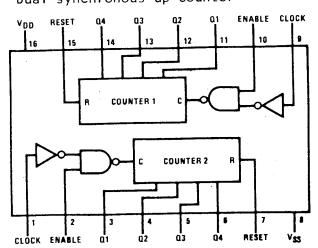

The two octave phase locked keyboard is available in two versions - option 05, mono, for controlling one Harmonizer, and option 06, polyphonic, for controlling one, two, or three Harmonizers. The mono keyboard cannot be 'upgraded' to polyphonic.

The keyboard controls the pitch ratio of the Harmonizer(s) in discrete musical steps. Middle C on the keyboard is 1.00 on the readout - a one-to-one pitch ratio (unison). Playing the E above middle C will give a harmony of a major third, playing E flat will give a minor third, and so on.

When the polyphonic keyboard is being used to control three Harmonizers, the first key pressed controls Harmonizer #1, the second key pressed (while holding the first) controls Harmonizer #2, and the third key pressed (while still holding the first and second) controls Harmonizer #3. Releasing any of these keys and pressing another will change the pitch of that Harmonizer only.

The keyboard GLIDE pot affects Harmonizer #1 only. The pitch change action ranges from instantaneous to a gentle slide. There is a LOCK switch for each Harmonizer, which holds the Harmonizer at the last note pressed. In non-LOCK mode, the Harmonizer(s) will return to middle C in the absence of any key depression.

No music is generated in the keyboard. Your music, passing through the Harmonizer, is pitch changed on instruction from the keyboard. The keyboard/Harmonizer combination can be used as a musical instrument if the Harmonizer input is supplied with middle C (approximately 260 cycles) of the waveform or timbre you require.

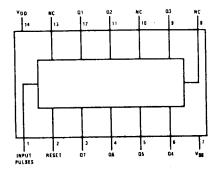

The keyboard is basically an electronic clock, with some sequencing and timing circuitry. The keyboard is slaved to the Harmonizer clock (Harmonizer #1 for the poly keyboard) for perfect unison at middle C. Keyboard keys select appropriate timing pulses, which command the desired pitch change in the Harmonizer.

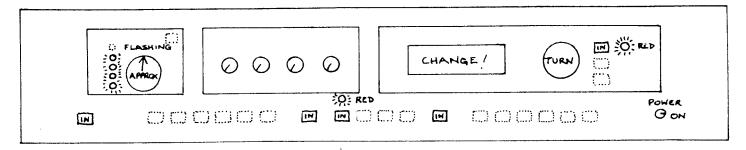

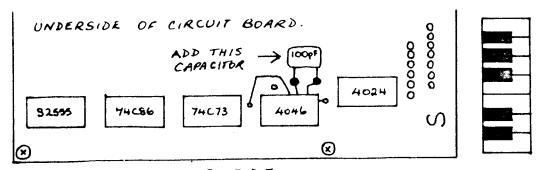

#### Use of the HK940 Keyboard with Model H949 Harmonizer

The H949 Harmonizer can lower the pitch of an input signal by two octaves. The keyboard does not control this lower octave.

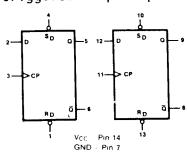

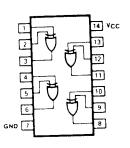

For use with the H949 Harmonizer, the keyboard requires the following modification. With keys towards you, loosen the left wooden side enough to allow removal of the top cover. Underneath is the underside of the circuit board. Add a 100 pF DM15 capacitor, as shown. Replace the top cover, and tighten the left side.

LEFT SIDE

NOTE: If the keyboard was supplied with a 949 Harmonizer, this modification is not necessary.

#### INTERCONNECTION OF HK940 KEYBOARD WITH EVENTIDE HARMONIZER MODELS H910 & H949

- 1. Harmonizer with mono keyboard, and Harmonizer #1 with poly keyboard, should be equipped with a keyboard socket on the Harmonizer rear panel.

- a) If no socket is supplied, ask your dealer to provide one. NOTE: every H949 is fitted with a socket already.

- b) If the socket is supplied but not installed, proceed as follows:

- i. screw socket into rear panel of Harmonizer (remove blanking plate).

- ii. plug connector M3 together (observe polarity).

- iii. remove shorting connector from M4. KEEP IT SAFELY! It will be needed if you ever require to use the Harmonizer with a synthesizer keyboard or similar.

- iv. plug connector M4 together (observe polarity).

- c) Connect keyboard cable to socket on Harmonizer rear panel.

- d) H910: Press KBD switch on Harmonizer front panel.

H949: Select KEYBOARD control mode on Harmonizer front panel.

- 2. Harmonizer #2 or #3 with poly keyboard

- a) For H910 Harmonizers only: If Harmonizer has a keyboard socket, this must be disconnected from M3 and M4, and shorting plug replaced on M4 (observe polarity).

- i. If you have lost the shorting plug, the two pins to be shorted together are (counting the pin nearest the front panel as #1) pin #2 and pin #3.

- b) A cable which is phone plug to two lug connectors is supplied. Connect phone plug to jack H2 or H3 on keyboard rear panel.

- H910: Connect red lug to terminal 3 of Harmonizer (see page 3 of manual: terminal 3 is Remote Control Frequency IN).

Connect black lug to terminal 4 of Harmonizer (Remote Control GROUND).

- H949: Connect red lug to terminal 9 of Harmonizer (External Control FROM KYBD).

Connect black lug to terminal 10 of Harmonizer (External Control GROUND).

- c) H910: Press KBD switch on Harmonizer front panel. H949: Select KEYBOARD control mode on Harmonizer front panel.

# Eventide's harmonizer model H949

# TECHNICAL SECTION

TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | , page                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| ALIGNMENT INSTRUCTIONS  Audio Alignment Compressor Distortion and Level Adjustment Offset Adjust Main Output Distortion and Level Adjustment Delay Output Distortion and Level Adjustment Feedback Level Timing and Control Alignment Master Oscillator Tuning Manual Control External Control Voltage Single Sideband Generator Tape Capstan Drive Flange Symmetry                                                                                     | T1. T1. T1. T1. T1. T1. T2. T2. T2. T2. T2. T2. T3.                              |

| SERVICE SECTION Introduction Power Supply Rear & Right Side Panel Wiring Harnesses                                                                                                                                                                                                                                                                                                                                                                      | T3.<br>T4.<br>T4.                                                                |

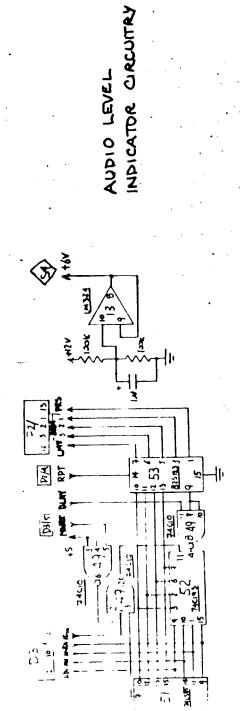

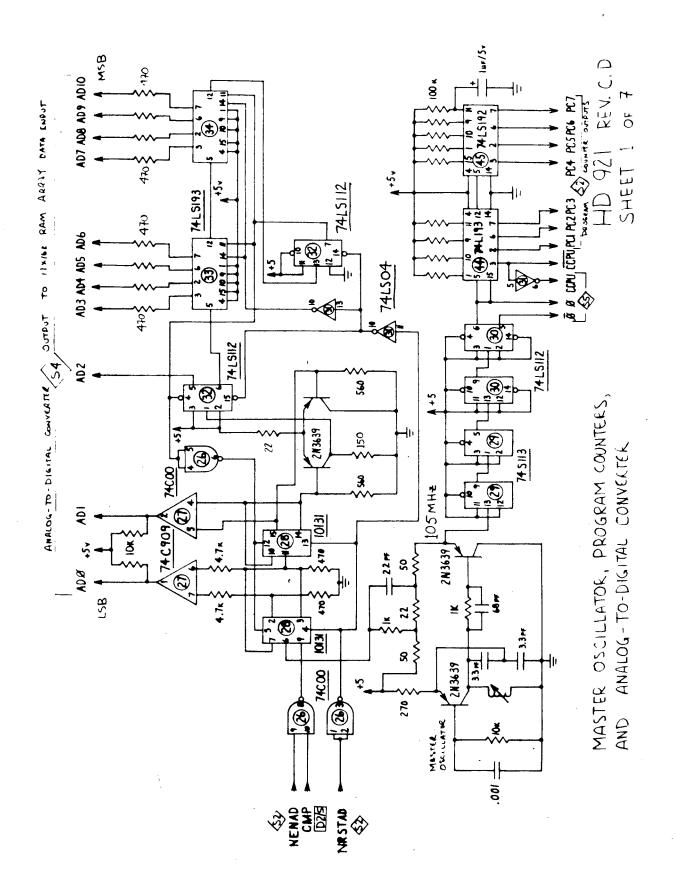

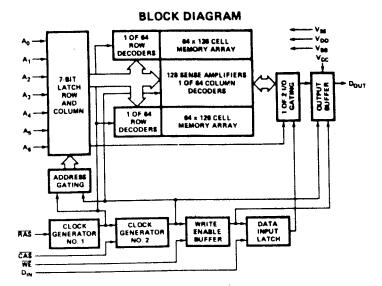

| HA931 - LOWER P. C. BOARD  Block Diagram Audio Processing Input Processing Output Processing Pitch Change Timing and Control Circuitry Read FIFO Clock Select Voltage Controlled Oscillator (VCO) VCO Control - Manual VCO Control - CV + Manual VCO Control - Keyboard Remote Control Voltage Single Side Band Generator (SSB) Voltage Controlled Quadrature Oscillator Pseudo Random Noise Generator Tape Capstan Drive Delay Set Audio Level Display | T5.<br>T6.<br>T6.<br>T6.<br>T7.<br>T7.<br>T7.<br>T8.<br>T8.<br>T8.<br>T9.<br>T10 |

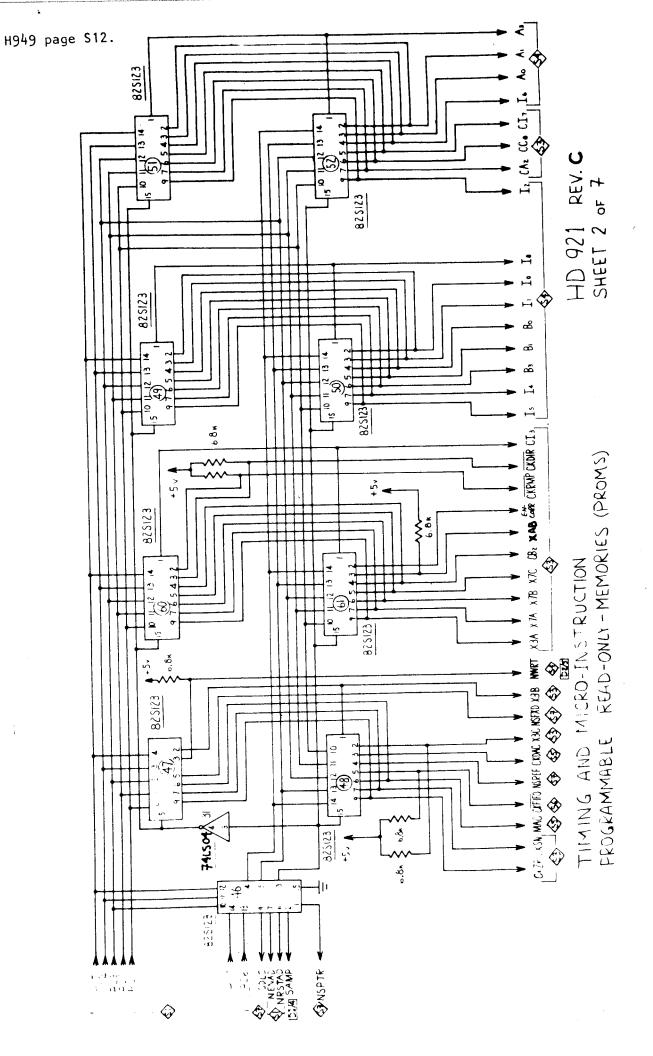

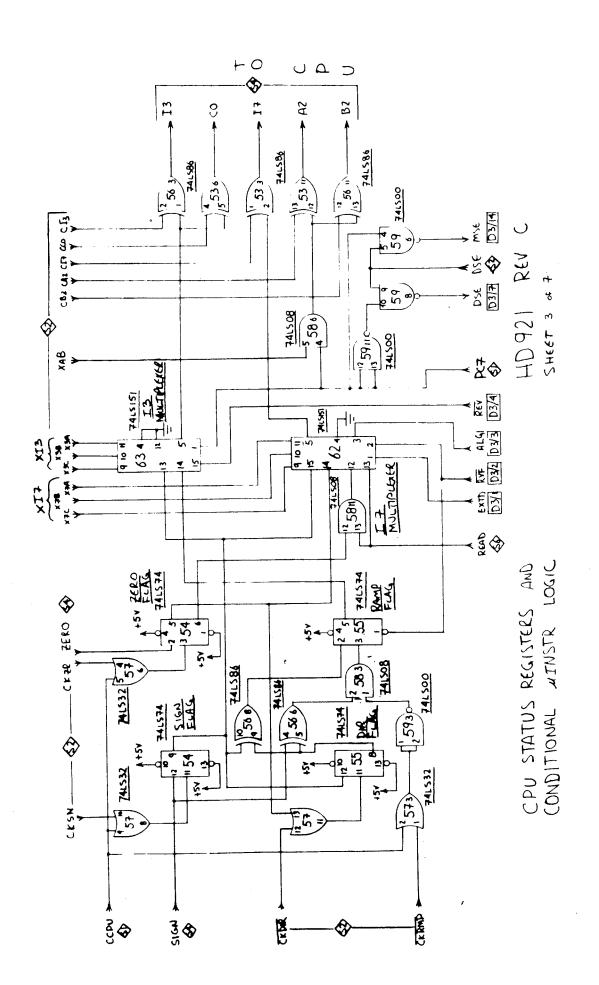

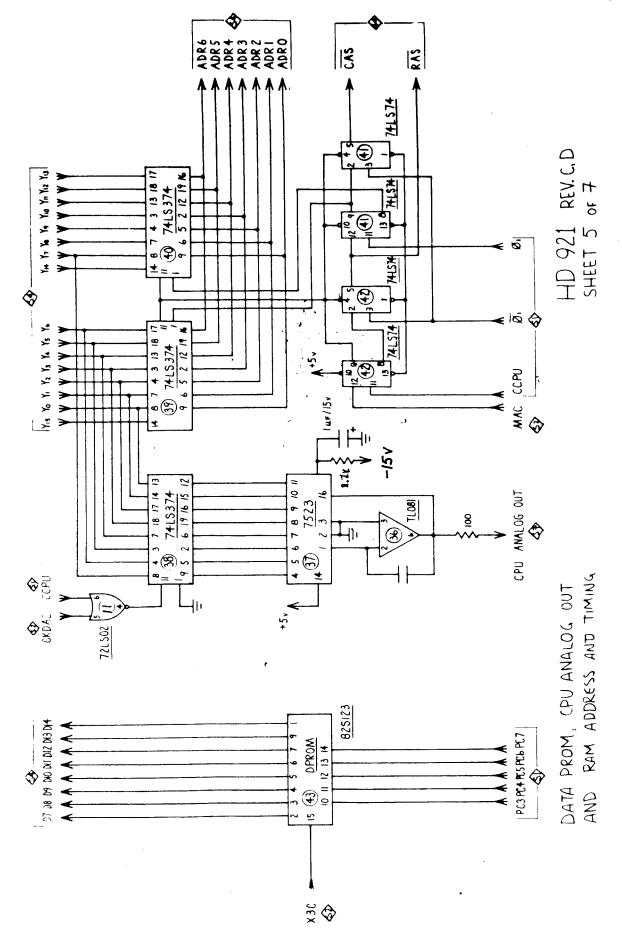

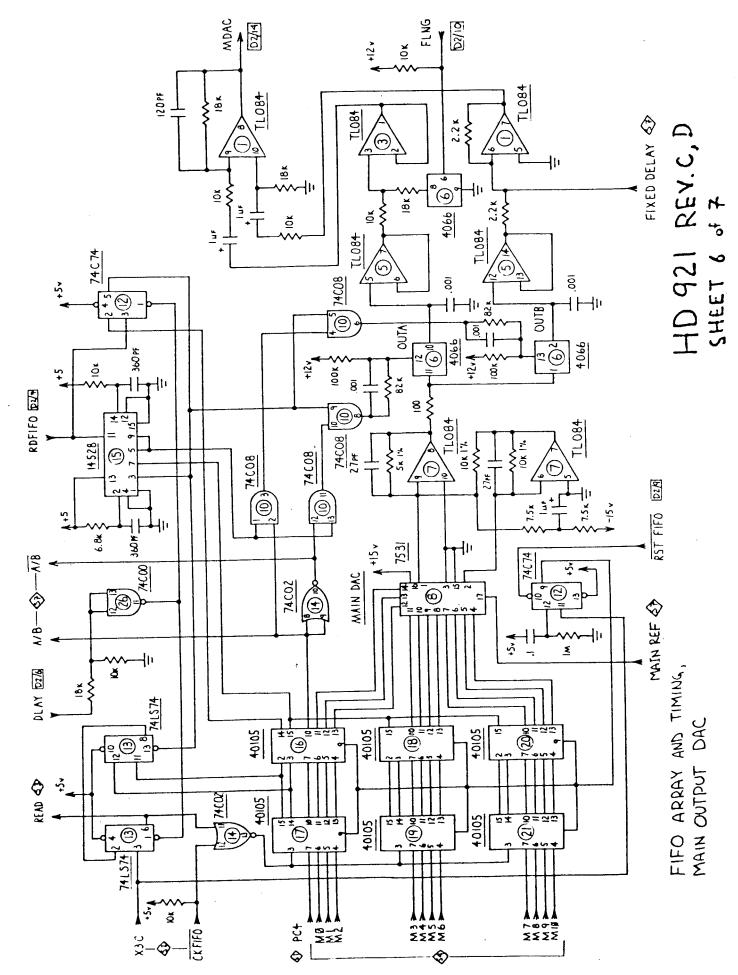

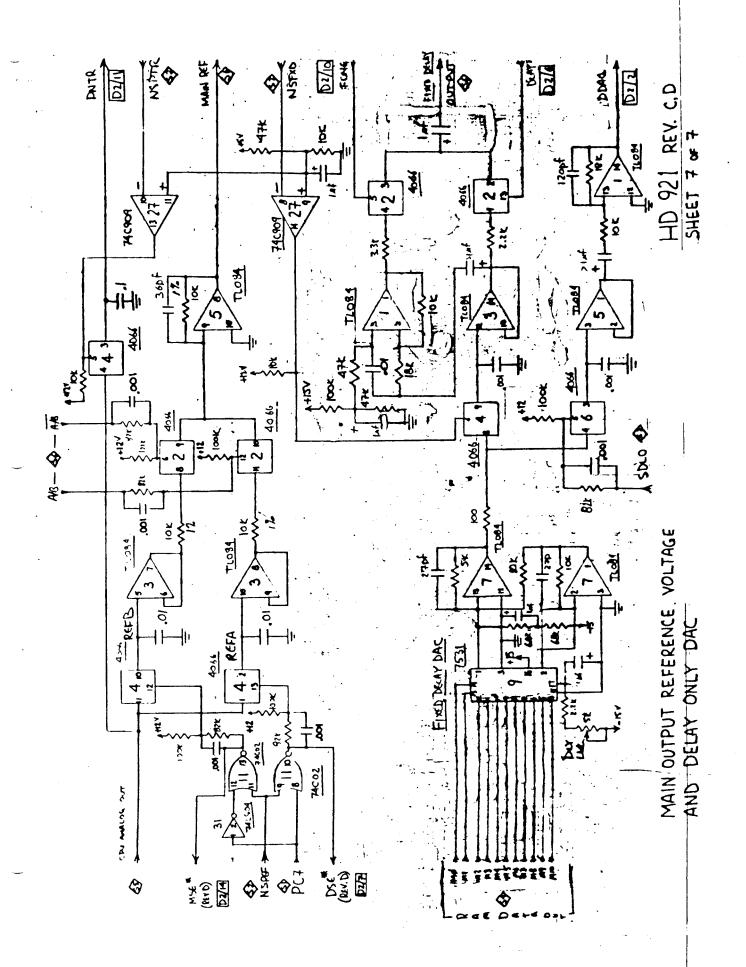

# HD921 - UPPER P. C. BOARD

| Block Diagram Master Oscillator Program Counters Timing PROM Central Processing Unit (CPU) Micro-Instruction (uINST) PROMS Conditional Micro-Instructions Conditional CPU Register Addresses Status Flags CPU Data Input CPU Analog Output 11 x 16 K Dynamic RAM Array Analog-to-Digital Converter (ADC) Delay Only Output Fixed Delay Output First-In First-Out (FIFO) Registers Main Output DAC Main Output Reference Voltage Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T13.<br>T14.<br>T14.<br>T14.<br>T15.<br>T16.<br>T17.<br>T17.<br>T17.<br>T18.<br>T18.<br>T19.<br>T19.<br>T19.<br>T20.<br>T20.                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

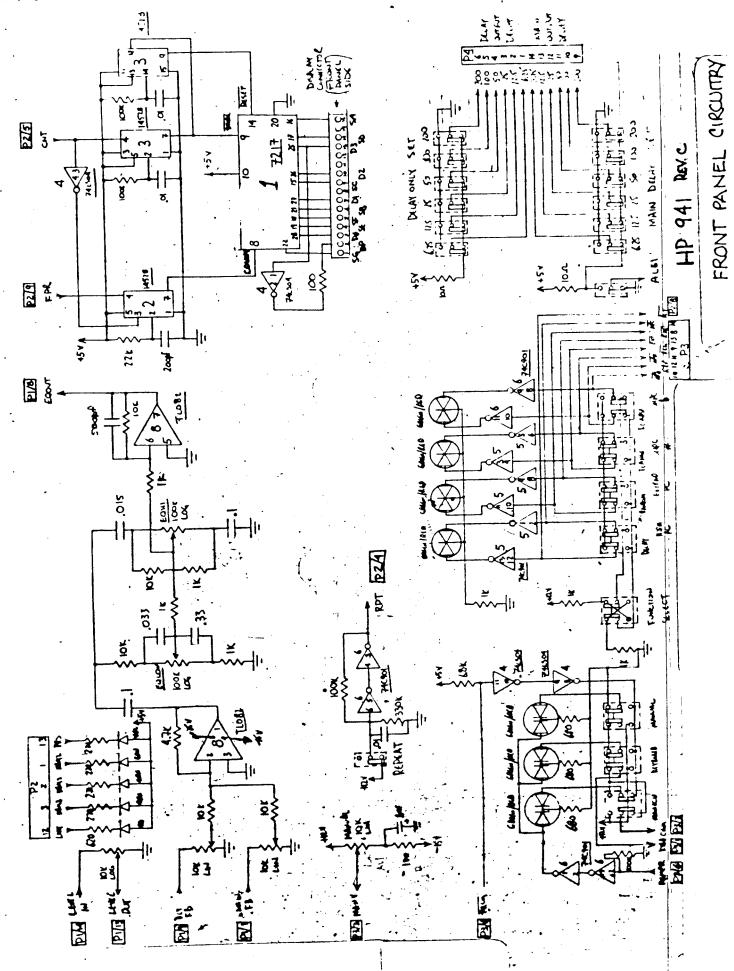

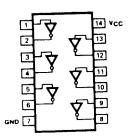

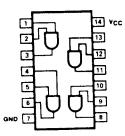

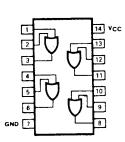

| HP941 - FRONT PANEL BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | T21.                                                                                                                                                          |

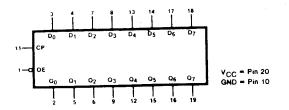

| Input Level Feedback Delay Set Switches Function Select Algorithm Select Control Mode Select Pitch Ratio Readout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T21.<br>T21.<br>T21.<br>T21.<br>T21.<br>T21.<br>T22.                                                                                                          |

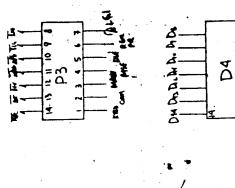

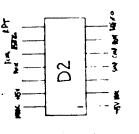

| BLOCK DIAGRAMS AND SCHEMATICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |

| Master Block Diagram Input Audio Processing (block diagram) Output Audio Processing (block diagram) Pitch Change Timing and Control (block diagram) System Timing and Central Processing Unit (block diagram) Input Audio Processing Output Audio Processing Voltage Controlled Oscillator and FIFO Clock Select Single Side Band Generator Function Select Logic, Delay Set Logic, Pseudo Random Noise Generator, Capstan Drive and Display Timing Circuitry Audio Level Indicator Circuitry DIP Connectors Power Supply Master Oscillators, Program Counters, and Analog-to-digital Converter Timing and Micro-Instruction PROMS CPU Status Registers and Conditional uINST Logic 16-Bit CPU and 11 x 16 K Dynamic RAM Array Data PROM, CPU Analog Out and RAM Address and Timing FIFO Array and Timing, Main Output DAC Main Output Reference Voltage and Delay Only DAC HP941 Front Panel Circuitry | \$1.<br>\$2.<br>\$3.<br>\$3.<br>\$4.<br>\$5.<br>\$6.<br>\$7.<br>\$8.<br>\$9.<br>\$10.<br>\$11.<br>\$12.<br>\$13.<br>\$14.<br>\$15.<br>\$16.<br>\$17.<br>\$18. |

APPENDIX - Integrated Circuits used in the H949 Harmonizer APPENDIX - Ribbon Cable Harnesses in H949 Harmonizer

# ALIGNMENT INSTRUCTIONS

The trimpots referred to in the following instructions may be located on the 949's circuit boards by consulting the topological drawing in the section on each board.

#### AUDIO ALIGNMENT

NOTE: For the following adjustments both FEEDBACK level controls should be OFF, DELAY should be set to zero for each output, and ALGORITHM 2 should be selected unless otherwise indicated.

#### COMPRESSOR DISTORTION AND LEVEL ADJUSTMENT

- 1) Apply a +6dBm 1kHz low-distortion sine wave to the 949.

- 2) Turn the INPUT LEVEL knob until the sine wave appears clipped at the COMPRESSOR input.

- 3) Reduce the input signal level by 3dB.

- 4) Adjust the COMPRESSOR GAIN trimpot (G) so that the red LIMIT LED just begins to light.

- 5) Attach the distortion meter to the COMPRESSOR output.

- 6) Adjust the HIGH FREQUENCY DISTORTION trimpot (H) for minimum distortion.

- 7) Reduce the input sine-wave frequency to 100Hz.

- 8) Adjust the LOW FREQUENCY DISTORTION trimpot (L) for minimum distortion.

- 9) Repeat steps 4-8 as necessary.

#### OFFSET ADJUST

- 1) Apply a 1kHz, +6dBm sine-wave to the 949.

- 2) Adjust the INPUT LEVEL pot so that the LIMIT LED begins to light.

- 3) Reduce the input signal level by 45dB.

- 4) Adjust the OFFSET trimpot so that the yellow PRESENT LED just turns off or is flickering.

NOTE: If a significant adjustment of the OFFSET trimpot (greater than 10 degree rotation) is necessary, the COMPRESSOR DISTORTION AND LEVEL ADJUSTMENT should be repeated.

#### MAIN OUTPUT DISTORTION AND LEVEL ADJUSTMENT

- 1) Select MAIN OUTPUT RANDOM FUNCTION, KEYBOARD CONTROL MODE (PITCH RATIO should read 1.000).

- 2) With a 1kHz signal applied to the input, set the INPUT LEVEL pot so that the top GREEN level LED just begins to turn on.

- 3) Adjust the MAIN OUTPUT EXPANDER GAIN trimpot (G) for a peak-to-peak swing of 16 volts.

- 4) Adjust the HIGH FREQUENCY trimpot (H) for minimum distortion.

- 5) Reduce the input frequency to 100 Hz.

- 6) Adjust the LOW FREQUENCT trimpot (L) for minimum distortion.

- 7) Re-adjust the GAIN trimpot for a 16 volt output swing.

- 8) Select DELAY FUNCTION.

- 9) Adjust the DELAY LEVL trimpot on the top board, HD921, for a 16 volt output swing.

#### DELAY OUTPUT DISTORTION AND LEVEL ADJUSTMENT

Follow steps 1 - 7 described above for MAIN OUTPUT.

H949 page T2.

#### FEEDBACK LEVEL

- 1) Select MAIN OUTPUT DELAY FUNCTION.

- 2) Apply a 1kHz input signal with sufficient level to light the LIMIT LED.

- 3) Set MAIN DELAY equal to 200 msec.

- 4) Set both FEEDBACK EQ pots to FULL CUT.

- 5) Turn MAIN FEEDBACK LEVEL pot full clockwise.

- 6) Turn INPUT LEVEL pot off (counter clockwise) and observe output signal.

- 7) Adjust FEEDBACK LEVL trimpot so that output decays gradually.

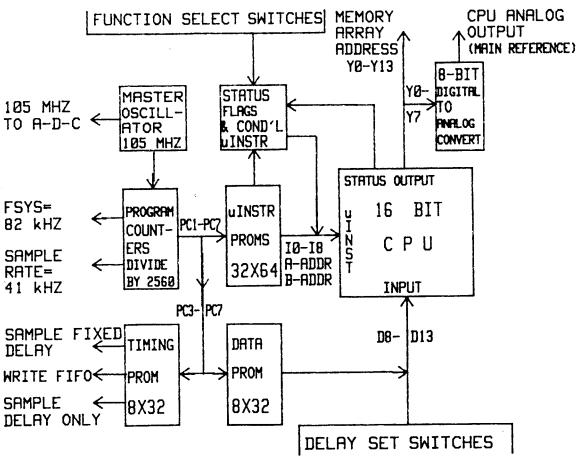

#### TIMING AND CONTROL ALIGNMENT

The following alignment instructions should be followed carefully and in the indicated sequence to assure proper performance.

#### MASTER OSCILLATOR TUNING

- 1) Connect frequency counter (or 'scope) to PIN 7 of IC47.

- 2) Swing board up and adjust COIL (variable inductor) using a plastic hex alignment tool for a frequency of 40.96kHz CAUTION-Take care not to crack the brittle tuning slug.

#### MANUAL CONTROL

- 1) Select NORMAL pitch change mode and MANUAL CONTROL MODE.

- 2) Rotate MANUAL pot fully counter-clockwise and adjust trimpot MINF, located on front panel board HP941 for a PITCH RATIO of approximately .240.

- 3) Rotate MANUAL pot fully clockwise and adjust trimpot MAXF, located on lower board HA931, for a PITCH RATIO of approximately 2.10.

- 4) Repeat steps 2 & 3 as necessary.

#### EXTERNAL CONTROL VOLTAGE

- 1) Select NORMAL pitch change mode and MANUAL CONTROL MODE.

- 2) Adjust MANUAL pot for PITCH RATIO of 1.00.

- 3) Select CV+MAN CONTROL MODE.

- 3) Apply minimum desired control voltage to the rear panel terminal strip input CV IN.

- 4) Adjust trimpot ECV OFFSET for a PITCH RATIO of .500

- 5) Apply maximum desired control voltage to CV IN.

- 6) Adjust trimpot ECV LEV for a PITCH RATIO of 2.00

- 7) Repeat steps 3, 4, 5 & 6.

The 949 is factory adjusted for a +12 volt to ground ECV range so that the pitch can be controlled by an external potentiometer connected to the BIAS OUT rear panel terminal.

#### SINGLE SIDE BAND GENERATOR

NOTE: This adjustment should not be performed without using a SPECTRUM ANALYZER capable of resolving an  $82 \, \text{kHz}$  signal with 300Hz sidebands. Fortunately this adjustment is not very critical; re-adjustment should be necessary only if one of the modulator IC's (IC's 38 & 39) is replaced.

- 1) Set SPECTRUM ANALYZER for a center frequency of 82kHz and resolution of 300Hz.

- 2) Attach SPECTRUM ANALYZER to PIN 1 of IC41.

- 3) Select uPC# function and MANUAL CONTROL MODE with the MANUAL pot set at twelve o'clock.

- 4) Null 82kHz signal by alternately adjusting trimpots SSB1 and SSB2.

- 5) Select uPCb.

- 6) Repeat step 4.

#### TAPE CAPSTAN DRIVE

- 1) Disconnect keyboard (if necessary).

- 2) Select KEYBOARD CONTROL MODE.

- 3) Connect frequency counter (or 'scope) to the 19.2kHz CAPSTAN DRIVE terminal strip output.

- 4) Adjust trimpot CAP CAL for 19.2kHz

#### FLANGE SYMMETRY

In the FLANGE mode a fixed delay is added to (mixed with) a pitch changed signal. The pitch changed signal's delay slowly varies between two fixed delay points. The center of this delay range should be equal to the fixed delay. When the two delays are equal maximum cancellation results. This effect is most apparent when the input program material is broadband noise.

- 1) Apply a noise signal (white, pink or whatever) to the 949's audio input and set INPUT LEVEL properly.

- 2) Select FLANGE mode, MANUAL CONTROL MODE, and zero delay.

- 3) Set MANUAL pot to twelve o'clock.

- 4) Monitor the MAIN OUTPUT (speakers, for instance)

- 5) Adjust trimpot FLANGE SYM for symmetrical flanging about the maximum cancellation point.

# SERVICE SECTION

#### INTRODUCTION TO SERVICE SECTION

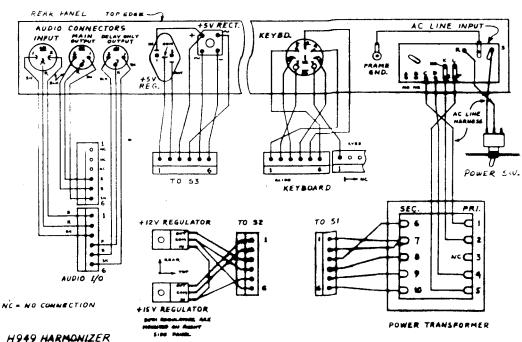

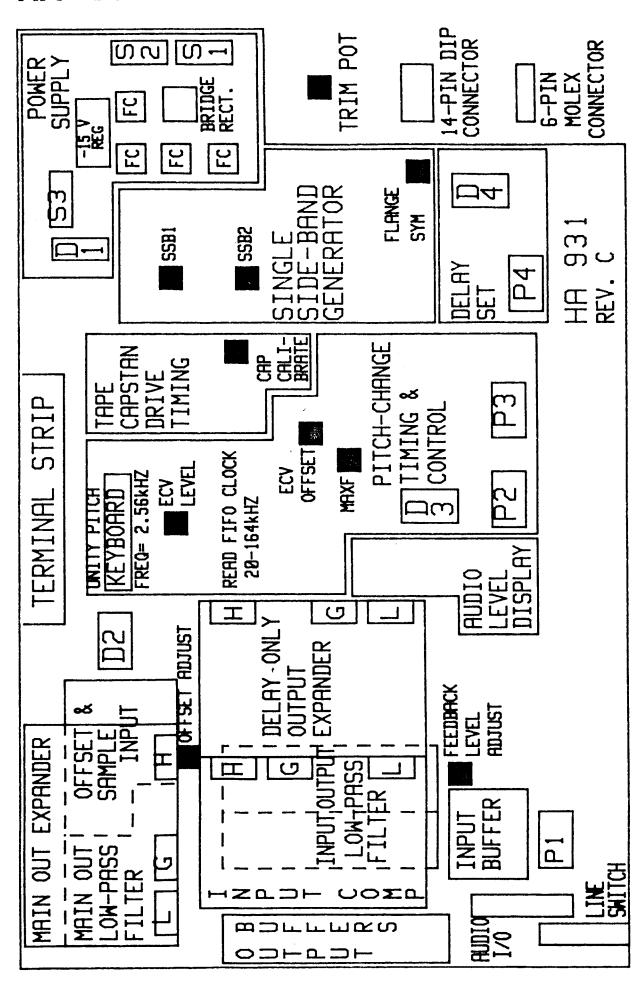

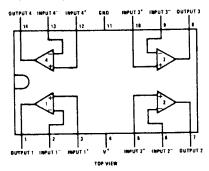

The circuitry of the H949 is contained on three printed circuit boards, with the exception of the unit's power transformers, a bridge rectifier, and three of the voltage regulators. These components are mounted on the right side and rear panels of the chassis. The part numbers of the three circuit boards are:

- 1) HA 931 Rev \_\_-Mounted horizontally on the bottom of the chassis. HA 931 contains power supply, audio processing, pitch change timing and function control circuitry. It is attached to the chassis at the rear panel terminal strip and to the bottom cover by 8 size 4-40 screws.

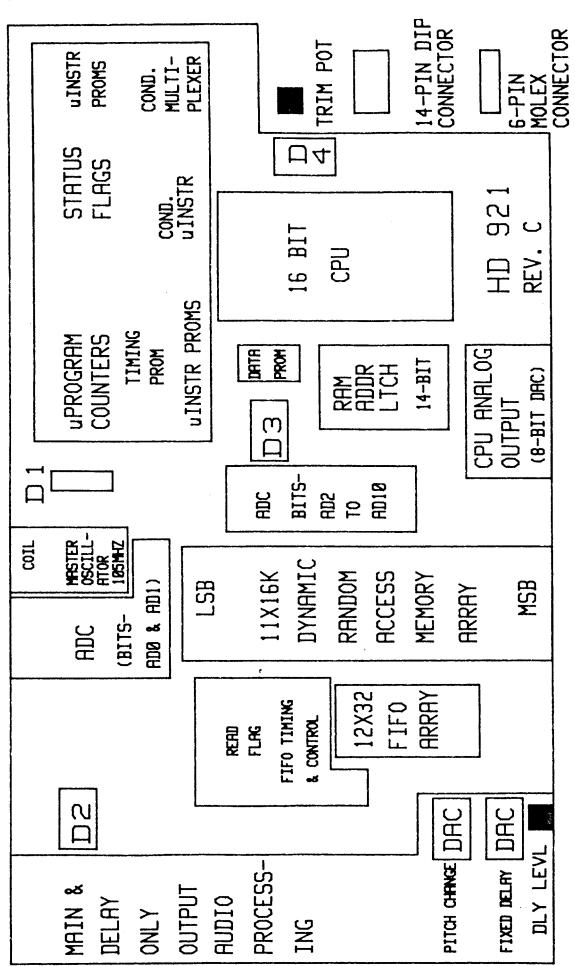

- 2) HD 921 Rev \_\_-Supported by five stand-offs above HA931 and attached to the rear panel by two hinged stand-offs. When the five size 6-32 screws are removed HD 921 can be swung up on its hinges allowing "power-on" access to the lower and front panel boards.

- 3) HP 941 Rev \_ -Mounted vertically behind and attached to the front panel by six stand-offs, it supports all front panel switches with the exception of the line and power switch. It also supports the PITCH RATIO READOUT and all indicator LEDS. Mounted on HP 941 is the following: AUDIO FEEDBACK, READOUT timing and DELAY SET circuitry.

#### POWER SUPPLY

The 949's power supply provides regulated +15, -15, +12 and +5 DC volts to the circuitry contained on the three p.c. boards. The power supply circuitry is mounted on lower p.c. board HA 931 and the right and rear chassis sides.

The AC input receptacle is mounted on the rear panel and accepts a standard IEC line cord. The receptacle also contains the unit's 1/2 amp "slow-blow" fuse (3/8 amp for 230 volt operation) and a small plug-in circuit card which determines the operating line voltage. This permits conversion to and from 230 volts without removing the unit's covers.

Line voltage is connected to the POWER TRANSFORMER's primary windings (mounted on the right side of the chassis) via the front panel POWER switch. The power transformer has two secondary windings; one low voltage-high current for the +5 volt supply and the other high voltage-low current for +15, +12, and -15 volts. The secondary windings are connected to HA 931 via 6 conductor Molex connector S1.

The +5 volt winding is routed directly to Molex connector \$3 which is connected to a 5-amp bridge rectifier and 3-amp LM323 voltage regulator which are mounted on the rear panel heat sink. The rectifier output (approx. +8.5 volts unregulated) and the regulator output (regulated +5 volts) return to HA 931 via \$3. The rectifier output is connected to the electrolytic filter capacitor mounted on HA 931.

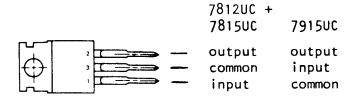

The other transformer secondary is connected to a bridge rectifier mounted on HA 931. Both a positive and negative rectified voltage are output from the bridge and filtered by a pair of electrolytic capacitors. The negative voltage is input to a 1/2-amp, -15 volt regulator, LM7915, mounted on HA 931. The positive rectified voltage is routed, via Molex connector S2, to two 1/2-amp positive voltage regulators, LM78M12 (+12 volts) and LM7815 (+15 volts), mounted on the right side of the chassis. The regulator outputs return via S2.

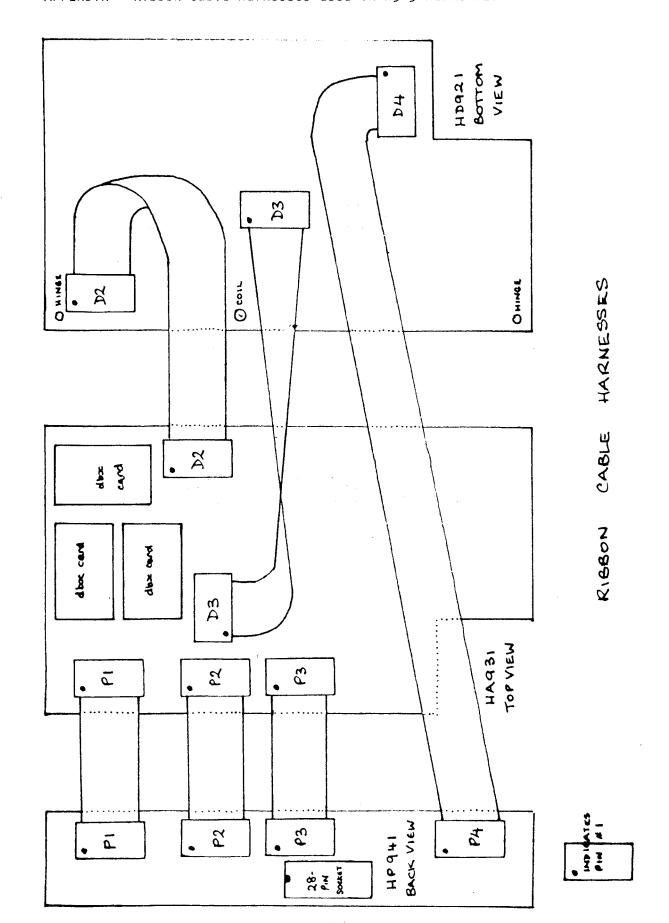

REAR AND RIGHT SIDE PANEL

WIRING HARNESSES

H949 page T6.

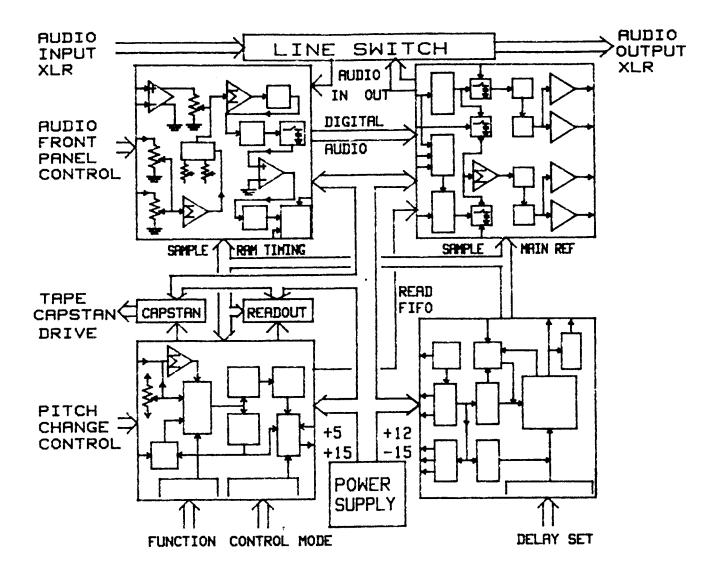

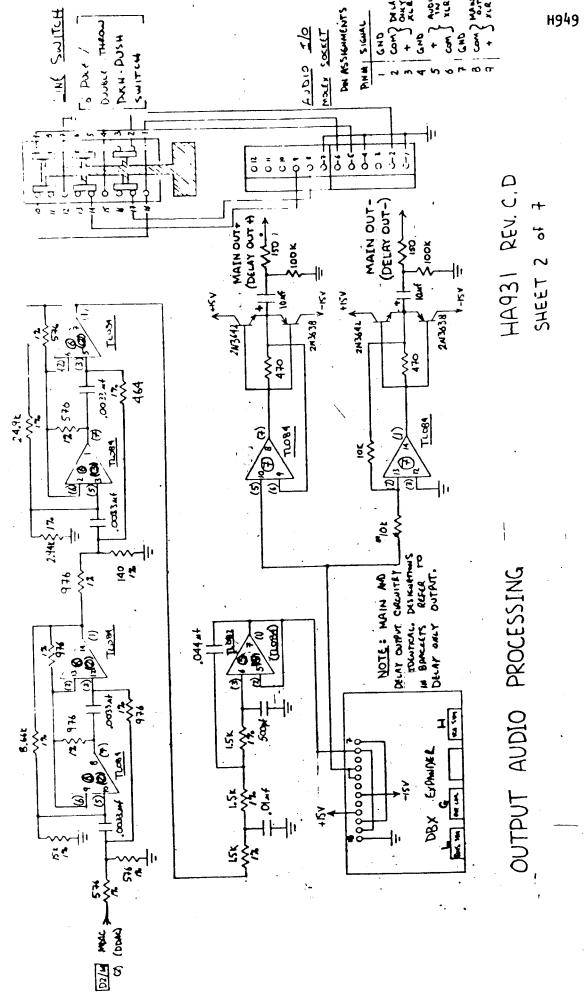

#### AUDIO PROCESSING

The three rear panel XLR connectors, AUDIO INPUT, MAIN OUT and DELAY ONLY OUT, terminate at a twelve-pin Molex connector AUDIO I/O, which is connected to the six-pole, double throw LINE SWITCH. When the switch is in the OUT position, the audio signal bypasses the unit by connecting the input XLR directly to both output XLR's, thus isolating the audio signal from the circuitry of the H949. This is an important diagnostic feature, allowing the user to test the external audio cables independently of the 949's circuitry. When the LINE SWITCH is IN, the audio input is applied to the 949, and the output XLR's are connected to the unit's output drivers.

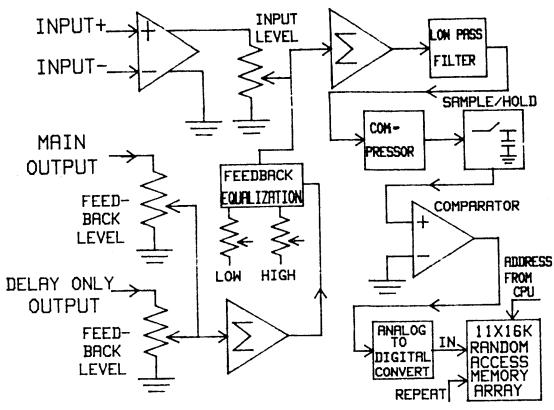

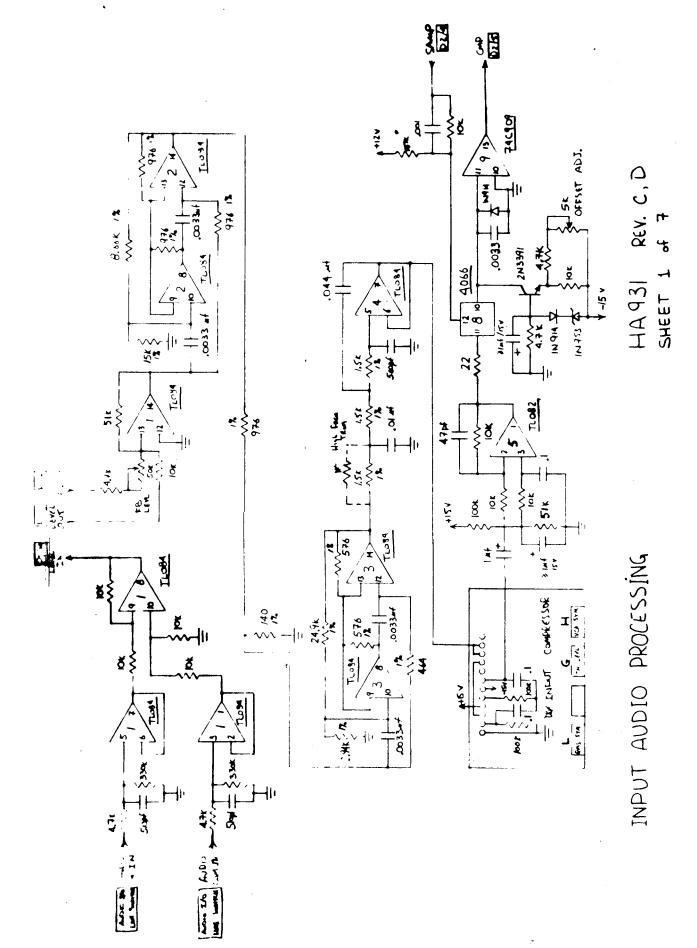

#### INPUT PROCESSING

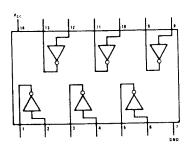

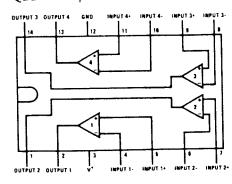

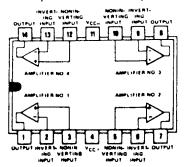

The differential input signal is buffered and converted to a single-ended signal by three of the op-amps of quad op-amp IC1. The signal is routed, via fourteen-pin connector P1, to the front panel and the INPUT LEVEL potentiometer. It returns via P1, and is summed with the FEEDBACK signal by the remaining op-amp of IC1. The signal is then low-pass filtered by a seven-pole, four-zero "Cauer-Chebychev" filter (one-half of quad op-amp IC's 2 and 3 and one-half of dual op-amp IC4) and compressed by a plug-in DBX 303 card (compression ratio 2/1). For proper adjustment of the DBX "distortion null" and "gain" trimpots, refer to the ALIGNMENT section of the manual. An AC-coupled inverting amplifier (one-half of IC6) superimposes a +5 volt DC bias on the signal, which is then sampled by analog switch IC8 and stored on the .001uF HOLD capacitor. Due to the unipolar nature of the analog switch, the audio signal is limited to a maximum voltage swing of 0 to + 10 volts. The sampled voltage stored on the HOLD capacitor is linearly discharged by a "constant current sink", (comprising a 2N3391 transistor, a 1N753 Zener diode, a 1N914 silicon diode, and associated passive components), while being compared to 0 volts by an analog comparator IC9. The comparator output signal, CMP, is a pulse whose width is proportional to the sampled voltage. The pulse-width modulated signal is then routed to the upper p.c. board HD921 where it is converted to a digital code as described later. Trimpot OFFSET ADJUST varies the HOLD capacitor discharge rate by varying the constant current sink. For proper adjustment of this trimpot refer to the ALIGNMENT section of this manual.

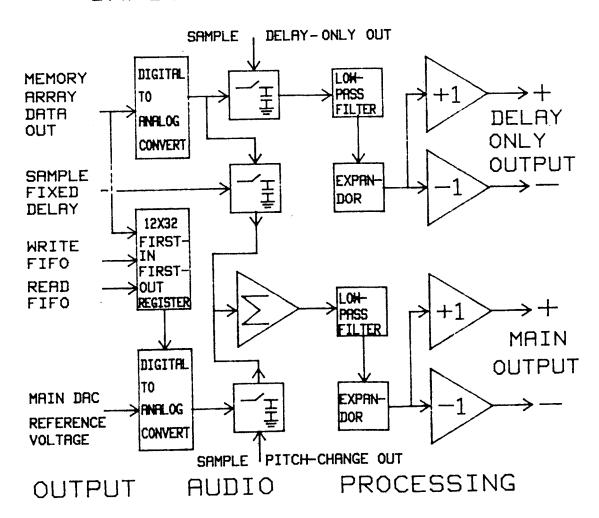

#### **OUTPUT PROCESSING**

The two output signals from connector D2, MDAC and DDAC, are applied to their respective low-pass filters, expanders, and output buffers. The main output signal MDAC is filtered by IC6 and one-half of IC5, expanded by a DBX 303 card (2/1 expansion ratio) and converted to a differential audio signal by one-half of IC7. Each phase of the output signal is driven by a complementary pair of transistors which provides greater output current capability into low impedance loads.

The DDAC output signal is processed identically to MDAC; filtered by one-half of IC's 2, 3 and 4, expanded by a third DBX card and converted to a differential audio signal (second-half of IC7).

#### PITCH CHANGE TIMING AND CONTROL CIRCUITRY

The pitch change functions of the 949 are accomplished by storing (or "writing") digitized audio at a fixed rate and retrieving it ("reading") at a variable rate. To increase pitch, one reads the data at a faster rate than that at which it was written; to decrease pitch, one reads the data at a slower rate than written. (The similarity to tape machine pitch change should be apparent). Of course matters are not quite this simple; there is a rub.

THE RUB: Let's suppose we are increasing the pitch of an audio signal as described above. We must remove data samples faster than we are storing them, eventually emptying our data store. At this point we are forced to stop outputting data and, not surprisingly, this does not sound very good. A moment's reflection will reveal that a similar problem arises when attempting to decrease pitch in this manner. This underlying physical dilemma must be resolved in some way by all "real-time" pitch changing devices; in most cases, this involves some form of splicing of the pitch changed signal. A number of schemes have been devised to perform this splicing; from "crummy and cheap" to "sophisticated and expensive". Our research has shown that the effectiveness of any splicing scheme (or splicing ALGORITHM) is highly program dependent. In general, an algorithm optimized for one class of signals (baroque music, for instance) will probably not work well on a different type of signal (e.g. speech).

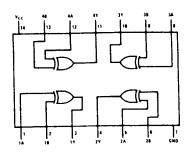

For this reason, two different splicing ALGORITHMS are available allowing the user to select the more effective in any given application. Both of the algorithms are based on splicing between two independently read, pitch changed signals designated OUTA and OUTB.

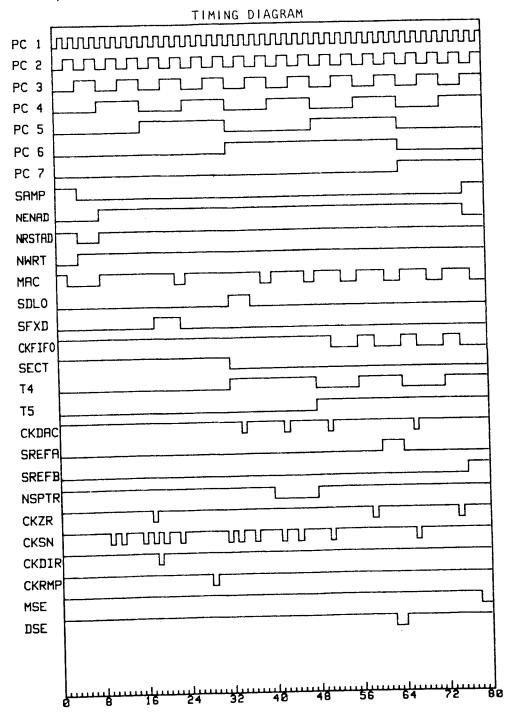

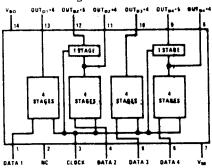

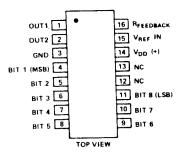

The pitch ratio of the 949 is determined by the rate at which data are read from the memory. The "write-data" rate is fixed and equal to the SAMPLING RATE, 41kHz. To achieve a three octave pitch change range, (two octaves down, one octave up), the "read-data" rate must vary from one-quarter to twice the "write-data" rate, that is, from 10.25kHz to 82kHz. The actual read-data rate of the 949 must be double these values (20.5kHz to 164kHz) because two pitch changed outputs are required.

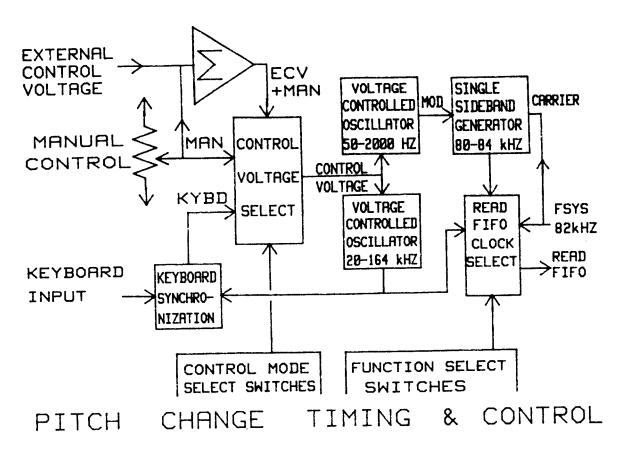

A large portion of the circuitry of the 949 is dedicated to providing the user with a wide range of controllable pitch change effects. All MAIN OUTPUT functions with the exception of the DELAY mode employ the pitch change capabilities of the 949. The degree of pitch change, equivalent to the PITCH RATIO, can be controlled from one of four sources; the front panel MANUAL control, an external KEYBOARD control (keyboard frequency range 1.28kHz to 5.12kHz for pitch ratios from .5 to 2), CV+MAN (an external control voltage summed with the MANUAL control), or (optionally) an intelligent remote controller (IEEE-488 bus).

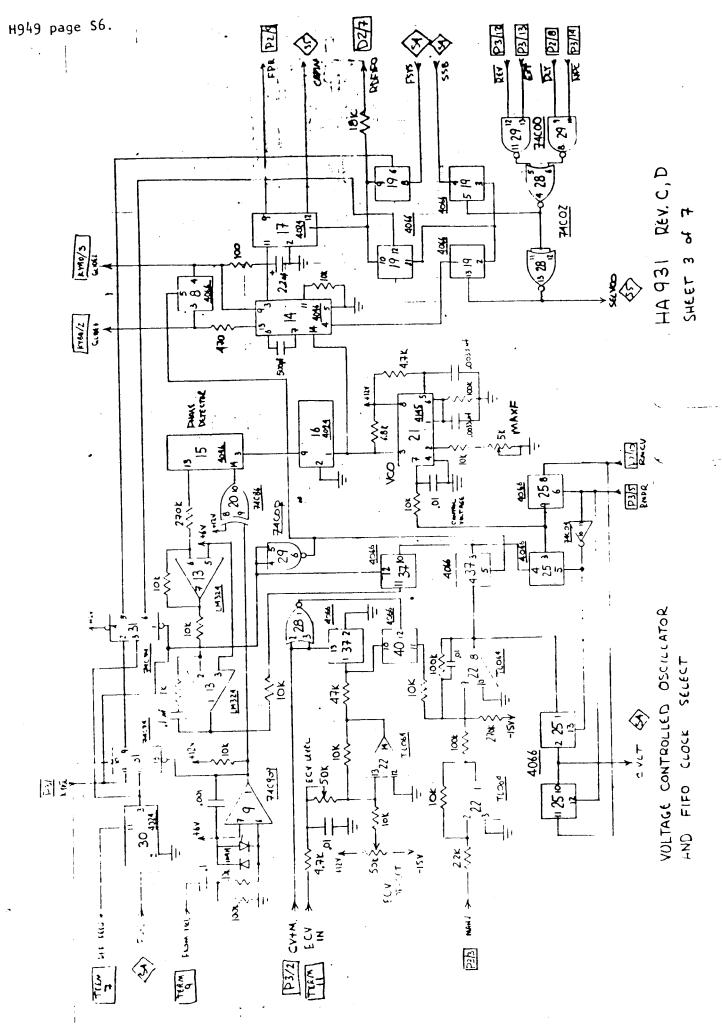

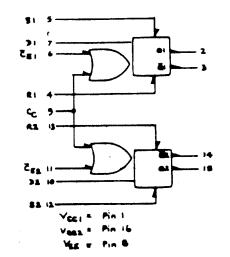

#### READ FIFO CLOCK SELECT

The clock signal which actually reads data from the FIFO ARRAY (and determines the pitch ratio) is designated the RDFIFO clock. The FUNCTION SELECT and CONTROL MODE SWITCHES determine whether the voltage-controlled oscillator (VCO), the single side band generator (SSB), the system clock (FSYS), or an external frequency source (KYBD) reads the FIFO ARRAY.

#### VOLTAGE CONTROLLED OSCILLATOR (VCO)

The VCO output is selected when in the NORMAL, EXTEND, REVERSE or DELAY mode. In the DELAY mode, the VCO has no effect on the output signal but is selected for PITCH RATIO indication, allowing the user to set the pitch ratio before switching to the pitch change mode. IC21 is a linear VCO biased to vary from 10.25kHz to 82kHz for an input voltage range of +1 to +10 volts. Phase-locked-loop IC14 and binary counter IC17 form a "frequency doubler" which multiplies the VCO output frequency by 2. This results in the desired frequency range, 20.5kHz to 164kHz. Trimpot MAXF can be used to vary the oscillator's maximum frequency (see ALIGNMENT).

The VCO can be controlled from the following sources:

1: MANUAL - The DC output (-15 to +12 volts) of the linear, front panel 10k ohm potentiometer is attenuated by an inverting op-amp (1/4 of IC22) and offset by a summing amp (1/4 IC22), resulting in a voltage range from +1 to +10 volts. In the MANUAL control mode this voltage is selected by analog switches IC's 25 and 37 and applied to the VCO.

H949 page T8.

- 2: CV+MAN This mode allows an external control voltage, connected at the rear panel terminal strip, to be added to the MANUAL control. Inverting op-amp, IC22, and a pair of 50k trimpots allow a wide range of control voltages to be accommodated. Trimpot ECV LEVEL varies the gain of the op amp allowing a small control voltage range to vary the pitch ratio over a wide range or alternately, a large control voltage range can be made to control pitch over a limited range. Trimpot ECV OFFSET allows the center of the external control voltage range to be varied. The trimpots are factory adjusted so that an external control voltage of from 0 to +12 volts results in a two octave variation of pitch ratio centered about the MANUAL control setting. (See ALIGNMENT for details.)

- 3: KEYBOARD The preferred means of externally controlling the pitch ratio is by an external oscillator with a frequency range of 1.28kHz to 5.12kHz. This results in a two octave pitch change range, -1/+1. In this control mode, the VC() is phase-locked to the external oscillator frequency resulting in precise pitch control with excellent long-term stability (providing, of course, that the external control frequency is stable). The KEYBOARD mode allows the pitch to be changed by precise musical intervals (25 notes over a two octave range), and is particularly useful for generating harmonies. Any keyboard instrument can be used to control the 949 if it meets the following requirements:

- a) The instrument must have a continuous output when a key is depressed

- b) The output frequency must vary from 1.28kHz to 5.12kHz.

- c) The waveform must have at least a 3 volt peak-to-peak swing

- d) The signal must be a "simple" waveform, e.g. sine, triangle or square wave. Ideally, the external frequency is generated by an EVENTIDE HK940 KEYBOARD. This keyboard controller assures ABSOLUTE stability by synchronizing to the 949's system clock. It also features a GLIDE (portamento) control, a LOCK-mode, which maintains the pitch-ratio of the last key pressed, and the ability to control up to three 949's independently and simultaneously.

When the KEYBOARD mode is selected, the VCO becomes part of a phane-locked-loop which locks to the external KYBD INPUT frequency. This external signal Is AC coupled to comparator IC9 whose square-wave output is one input to phase comparator IC15. The other input to the phase comparator is the VCO output frequency divided by 8 from IC16. The phase comparator output is low-pass filtered by the loop filter, comprised of one half of IC13. This results in the VCO running at precisely eight times the keyboard input frequency. When used with an EVENTIDE HK940 keyboard the time constant of the "frequency doubler" described above may be varied by the GLIDE potentiometer.

IC's 30 and 31 implement an important feature of the keyboard mode by detecting the absence of a keyboard input signal, such as when the keyboard is an organ or synthesizer and no keys are depressed. In this case, the pitch ratio is instantly set to unity (no delay change) by causing analog switch IC19 to select the system clock FSYS.

Apart from its function in keyboard operation, this feature is important in its own right. It allows the user to instantly "freeze" delay change in any of the pitch change modes by switching to the KYBD control mode with no keyboard input present. This is particularly useful in the FLANGE mode since it can be used to freeze the FLANGE at any stage.

REMOTE CONTROL VOLTAGE - Analog switch IC25 allows the pitch ratio to be OPTIONALLY varied by an intelligent controller interfaced to the standard IEEE-488 bus.

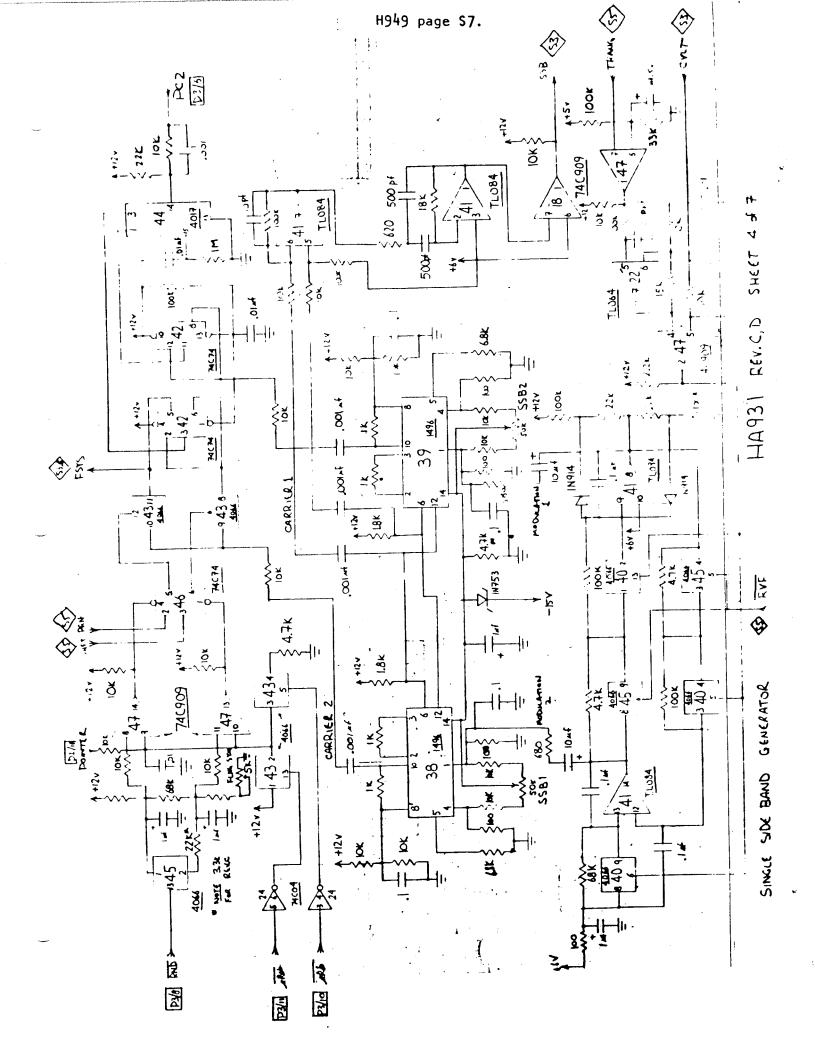

#### SINGLE SIDE BAND GENERATOR - SSB

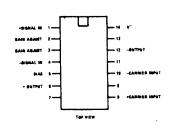

The SSB is selected in the uPC, FLANGE and RANDOM modes where stable, precise control of small pitch variations is desired. The circuitry of the SSB can be divided into three sub-sections: a pair of amplitude modulators, the carrier frequency generator, and the quadrature oscillator.

An amplitude modulator is a device which multiplies two analog signals. As per convention the higher frequency signal is called the CARRIER and the lower frequency signal the MODULATION. Theoretically if the carrier and modulation inputs are sine waves, the output will be the sum of two sine waves, one whose frequency is equal to the sum of the two input frequencies (CAR+MOD) and the other's equal to the difference of the input frequencies (CAR-MOD). These two signals are called the UPPER and LOWER SIDEBANDS.

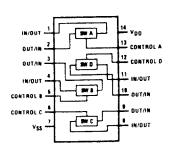

If two such modulators are connected so that the carrier inputs are of the same frequency but 90 degrees out of phase (in quadrature) and the modulation inputs are also in quadrature, then adding the two modulator outputs will yield only one sideband; either UPPER SIDE BAND (CAR+MOD) or LOWER SIDE BAND (CAR-MOD).

In the 949 the CARRIER input is FSYS (=82kHz) and the modulation is the output of a voltage controlled quadrature oscillator which can be varied from approx. 50Hz to 2000Hz.

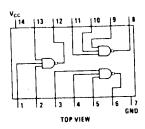

MODULATORS: IC's 38 and 39 are monolithic modulators which will accept an AC-coupled carrier input and an AC-coupled modulation input and generate a suppressed-carrier, sum and difference frequency output signal. Trimpots SSB1 and SSB2 can be adjusted to null the carrier component at the SSB output. (This adjustment should not be attempted without a spectrum analyzer; for details, see ALIGNMENT.) Each modulator has differential open-collector outputs which are cross-coupled and connected to the input of a difference amplifier (1/4 of IC41). This amplifier's output is band-pass filtered (1/4 of IC41) to remove spurious harmonics which are the result of the modulation process. The SSB signal is finally converted to a square wave by comparator IC18.

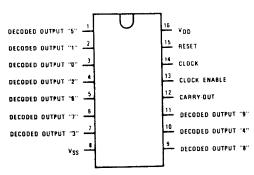

CARRIER FREQUENCY GENERATION: The carrier frequency of the SSB generator is derived from PC2, the 1.64MHz output of the uPROGRAM COUNTER located on the upper p.c.board, which is routed thru connector D3 (pin6). This TTL level signal is biased to drive 1044. a decoded output decade counter. Two of the ten 164kHz outputs, which are 180 degrees out of phase, drive dual data flip-flop IC42, each half of which is connected as a "toggle" flip-flop. The outputs of these flip-flops are a pair of 82kHz square waves which are 90 degrees out of phase. The output of one flip-flop, CARRIER 2, is applied to modulator IC39, while one of the two complementary outputs of the other flip-flop, CARRIER 1, is selected by a pair of analog switches, two quarters of IC43. Depending on which switch is turned on, CARRIER 1 will either LEAD or LAG CARRIER 2 by 90 degrees; which causes the SSB to generate either the UPPER or LOWER side band. Selecting the UPPER side band assures that the pitch ratio will be greater than unity while selecting the LOWER side band guarantees a pitch ratio lower than unity. One half of dual flip-flop IC46 determines which of the switches is selected. The flip-flop's state depends on a number of conditions, in particular the selected FUNCTION .

On "power-on" this circuit is synchronized by a pair of RC time constants which reset the decade counter IC44 and the dual flip-flop IC42. To insure proper sequencing the time constant of the counter is an order of magnitude greater than that of the flip-flops. It is possible, by switching the unit on and off rapidly, to throw this circuit "out of synch" rendering all SSB functions inoperative. To re-synch, turn the unit off for 10 seconds before re-applying power.

H949 page T10.

If either of the uPC (micro-pitch change) FUNCTIONS is selected, the appropriate switch of IC43 is enabled bringing one input of a pair of comparators, (1/2 of IC47), to either +12 or approx. +1 volts. This enables the appropriate comparator output which in turn sets or resets IC46 causing the SSB to generate the UPPER side band for uPC# and the LOWER for uPCb.